Armはなぜブランド名を変更するのか、「SME2」投入もAI対応に紆余曲折あり:Arm最新動向報告(17)(3/3 ページ)

Arm v9.3-AとSME2

以前、Arm v9-Aの詳細について本連載で説明したが、この時に見えていたのはArm v9.2-Aまでである。

ただこの時にはなく、後から追加されたものにSME(Scalable Matrix Extention)がある。これは、Armv9.2-AのオプションというよりもArmv9-Aそのもののオプションという扱いで2021年に発表され、仕様は2022年2月に公開されていた(図7)。

SMEを実装したのはApple M4が現時点で唯一の実在するプロセッサであり、ArmのCPU IPやQualcommなどの独自アーキテクチャの製品もこれをサポートしていない。このSMEというのは、SVE/SVE2の拡張版である。SVE/SVE2はいわば1次元のSIMD演算であり、行列に対して行や列の単位で、1行あるいは1列単位で処理を行っていく仕組みである。

これに対しSME2は2次元に拡張し、行列を一気に処理できる仕組みとなっている。ただし、初代SMEは外積を含む一部の行列演算の高速化のみに対応した、極めて限定された処理に向けたものだった。そこでより広範なアプリケーションに対応させるべく拡張されたのがSME2で、これがArm v9.3-Aで導入され、今回Lumex CSSと併せて発表された全てのC1 CPU(C1-Ultra/Premium/Pro/Nano)でSME2が利用できるようになった。

SME2は、新たに以下のような機能が追加されている。

- Zベクトルを乗数/被乗数入力とし、結果をZA配列ベクトルに蓄積するマルチベクトル乗算積算命令

- 複数のSVE ZA VectorをSource/Destination Registerとして使用し、ZA Vectorを利用するSME2命令の入力前処理/出力後処理を行うマルチベクトルロード/ストア/移動/置換/変換命令

- 従来のSVE Predication機構を拡張し、複数のVector Registerを制御できるPredicate-as-counter機構

- 専用ルックアップテーブル命令と外積命令を用いたNeural Networkの圧縮機能(Binary Neural Networkを含む)

- SME2のルックアップテーブル機能をサポートする512ビットのアーキテクチャレジスタZT0

ここで面白いのがこのSME2ユニットの利用方法である。SME2ユニットは膨大な数の演算ユニットを内蔵するので、CPUコアに収めるのは無理である。このため物理的にはCPUコアとは別になっている。

図3で、“C1 CPU Cluster”という左側の枠の中にC1-Ultra×2+C1-Pro×6があるが、それとは別にSME2とC1-DSUがクラスタ内に配される形だ。

Armの説明によれば、C1世代ではSME2の数は1つだが、次世代製品では2つになるらしい。さて、CPUコアとは別の場所にいるということはアクセラレータという扱いになるのかと思ったらそうではなく、全てのC1コアはSME2をデコード部で解釈可能であり、SME2命令が来た&クラスタ内にSME2ユニットがある場合は、そのままその命令をSME2にディスパッチして、以後の処理はSME2側で行われる。この際に行列全体をカバーするZA Vectorと呼ばれる拡張レジスタを利用して演算が行われる。

計算が終わったら、その結果をSVEレジスタに書き戻す(これはVectorのロード/ストア命令を使う)ことで結果をCPUパイプラインに戻す、という形になっている。要するに、CPUから見ると自身の演算ユニットで処理を行っているように見えて、その実は外にオフロードしているという実装になっている。これを行うため、C1 CPUにはSME2専用の実行パイプラインが用意されている。おそらくSME2ユニットと同期を取るのが目的だろう。

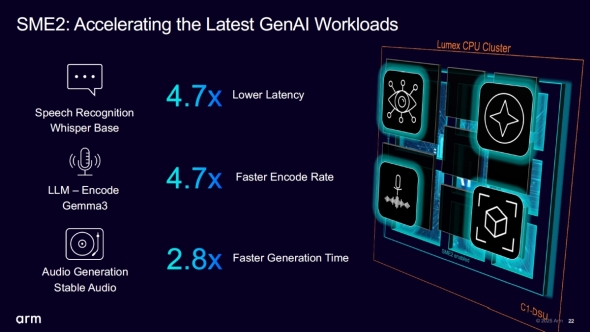

このSME2でAIの推論演算が2.8〜4.7倍高速化されたという話だが(図8)、ArmとしてはAI推論用にGPUやNPUを併用するという案が顧客に支持されなかったので、CPUにAI用アクセラレータを実装せざるを得なくなったということでもある。

マイクロコントローラー向けの分野では、それなりにNPUのEthosシリーズの採用事例が増えているが、こちらも競合製品が少なくないため普及しているとも言いにくい。そしてモバイル向けの場合、SoCベンダーが自前のNPUを提供するケースが多い。こうした状況でAI処理への対応を考えた場合、CPUそのものにAI処理のアクセラレータを内蔵させるのが一番得策であると考えたようだ。

ただし、実はこのSME2、既存のフレームワークとあまり互換性がない。以前ArmはArmNNと呼ばれるフレームワークを提供してきていたが、今回確認したところ「ArmNNはArm Compute Libraryを使用しており、Arm Compute LibraryはSME2の機能の一部のみをサポートしている。またCPU向けには今後は非推奨となっており、パートナーにはTFLite、Executorch、ONNX Runtimeなどのオープンソースのフレームワークへの移行を推奨している」という返事が戻ってきた。まだArmのAIに向けた取り組みには紆余(うよ)曲折が予想されそうである。

関連記事

- ≫連載「Arm最新動向報告」バックナンバー

Armのモバイル向け基盤が全面刷新で「Lumex」に、「SME2」でAI処理性能は5倍

Armのモバイル向け基盤が全面刷新で「Lumex」に、「SME2」でAI処理性能は5倍

Armがモバイル機器向けプロセッサIPセットの新たな演算サブシステム(CSS)プラットフォーム「Arm Lumex」を発表。CPUやGPUのブランド名を刷新するとともに、CPUクラスタにAIの演算処理を得意とする新たな拡張命令「SME2」を組み込むことでオンデバイスAIの処理性能を大幅に高めた。 AIデファインドビークルに向けた演算プラットフォームを発表

AIデファインドビークルに向けた演算プラットフォームを発表

Armは、AIデファインドビークルに向けた演算プラットフォーム「Arm Zena CSS」を発表した。自動車開発向けに標準化して統合したプラットフォームで、安全性を確保しつつ、ハードおよびソフトの開発期間を短縮する。 Armのクライアント機器向け最新ソリューション「TCS23」の全貌

Armのクライアント機器向け最新ソリューション「TCS23」の全貌

Armの最新動向について報告する本連載。今回は、2023年5月30日〜6月2日に開催された「COMPUTEX TAIPEI 2023」で発表されたクライアント機器向けの最新ソリューションである「TCS23」を構成する各IPを紹介する。 Armの次なる2000億個出荷に向けた布石「Arm Total Solutions for IoT」の狙い

Armの次なる2000億個出荷に向けた布石「Arm Total Solutions for IoT」の狙い

Armの年次イベント「Arm DevSummitの発表内容をピックアップする形で同社の最新動向について報告する本連載。今回は、2021年10月19〜21日にかけて開催された「Arm DevSummit 2021」について、「Arm Total Solutions for IoT」を中心に紹介する。 謎の多い「Armv9」について今分かっていることをまとめる

謎の多い「Armv9」について今分かっていることをまとめる

2021年3月末にArmが発表した最新命令セット「Armv9」。このArmv9について、これまでに公開された技術文書などを基に、現時点(2021年4月中旬)で判明していることをまとめた。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- ドローンやロボット向けの高性能で軽量なVLMを開発、8Bと2Bの2モデルを展開

- 大容量X線画像データを8600分の1に即時圧縮するFPGAデータ処理基板を共同開発

- 長期供給SoCを活用したMCU向け組み込みGUI開発ソリューションの提供を開始

- ドライブレコーダーの録画時間を最大10倍に延長する動画ソリューション

- 声やスマホでの操作も不要、次世代スマートホームは「ビルトイン型」へ

コーナーリンク