CFB技術と局所シールド技術で薄膜アナログICの3次元集積に成功:材料技術(2/2 ページ)

薄膜チップレット技術のプロセス

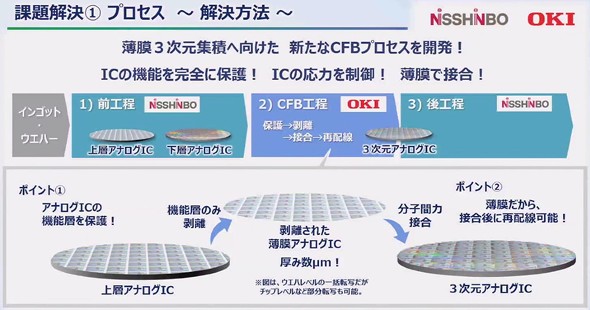

これらの課題を解消したのが今回の技術だ。同技術のプロセスは、まず日清紡マイクロデバイスの技術によりインゴット/ウエハーから上層アナログICと下層アナログICを作製する。

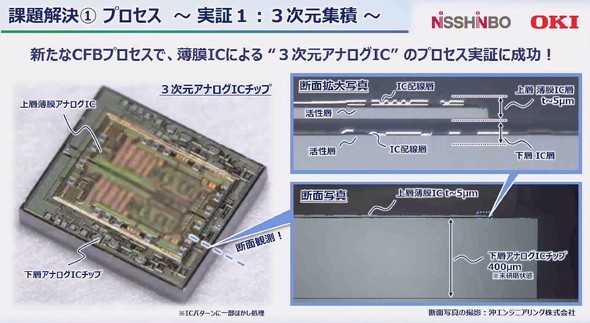

次に、新たなCFB技術のプロセスで、上層アナログICから厚み数μmの機能層を剥離する。この剥離した機能層を上層アナログICとして分子間力接合で下層アナログICに積層し3次元アナログICを作製。機能層は薄膜のため接合後に一般的なフォトリソグラフィー装置で再配線できる。

OKI グローバルマーケティングセンター CFB開発部 部長の谷川兼一氏は「CFB技術により薄膜のアナログICをガラス基板上に積層した後、フォトリソグラフィ装置で再配線することにも成功している」と語った。

続いて、作製した3次元アナログICに対して日清紡マイクロデバイスの技術により後工程でパッケージを行う。

プロセスにおける役割について、OKIはアナログICからの剥離と接合を担当し、日清紡マイクロデバイスは半導体前工程におけるアナログICの製造と後工程のパッケージを担う

局所シールド技術の機能

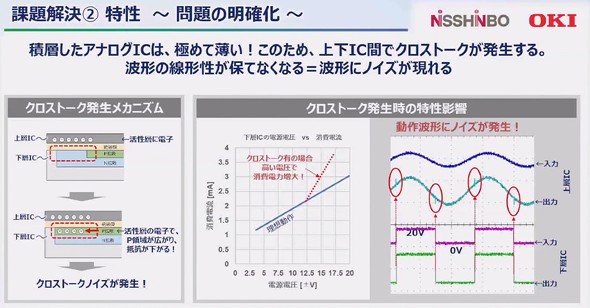

CFB技術により下層アナログICに積層した上層アナログICは薄いため、上下のアナログIC間でクロストークが発生する。クロストークとは回路あるいは伝送線からの信号が隣接する回路または伝送線に干渉しノイズを起こす現象だ。

緒方氏は「CFB技術で作製した3次元アナログICは上下のアナログICが近接するため、一方の回路が電流を受け動作すると、向き合っている回路で静電誘導が発生しクロストークが生じる。具体的には、上層ICの活性層に電子が流れると静電誘導が起き、近接する下層ICのP拡散層で+の電荷が誘起され−の電子が流れるようになる。これによりP拡散層が広がり電気抵抗が下がり設計より電気が流れクロストークが生じる」説明した。

下層のアナログICでクロストークが発生すると通常時と比べて消費電力が高くなる。上層ICの動作波形にもノイズが発生し信号処理が円滑に進まず搭載するデバイスの誤動作につながる。

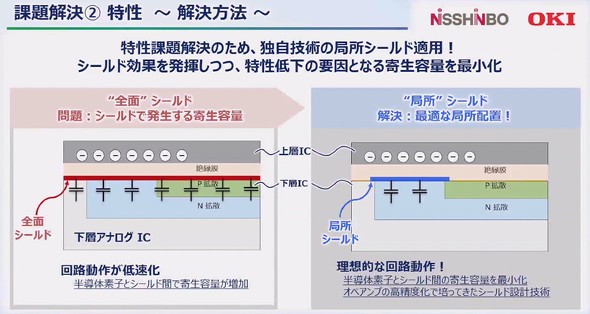

解決策として、日清紡マイクロデバイスがオペアンプの高精度化で培った局所シールド技術を活用する。局所シールド技術により、上層ICと下層IC間の一部に金属の薄膜を設けることで、半導体素子と金属薄膜間の寄生容量を最小化しつつ、クロストークを防ぐ。「上層ICと下層IC間の全面にシールドを設けると、回路動作の低速化を起こす寄生容量が増加するため、局所としている」(緒方氏)。

日清紡マイクロデバイスは局所シールド技術を適用した3次元アナログICの動作実証および測定を行った結果、上下のアナログICでクロストークがなく電力の増大もない理想的な動作を確認した。

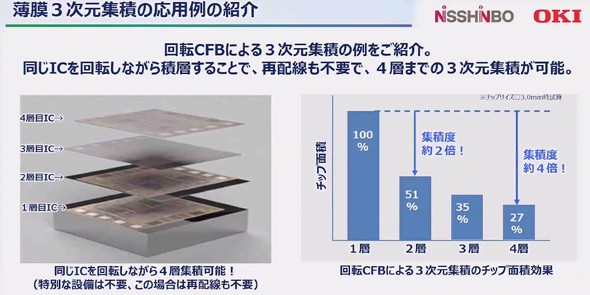

緒方氏は「CFB技術を応用し同様の薄膜ICを回転しながら積層することで、再配線や特殊な設備が必要なく4層まで3次元集積が可能なことも分かっている」と応用事例を紹介した。

関連記事

安価な縦型GaNを作れる新技術、QST基板のリサイクル技術も開発中

安価な縦型GaNを作れる新技術、QST基板のリサイクル技術も開発中

OKIと信越化学工業は、信越化学工業が独自改良したQST基板から窒化ガリウム機能層のみをOKIのCFB技術で剥離し、異種材料基板へ接合する技術について説明した。 最高レベルの過充電検出精度を持つリチウムイオン電池用ハイサイド保護ICを発売

最高レベルの過充電検出精度を持つリチウムイオン電池用ハイサイド保護ICを発売

日清紡マイクロデバイスは、1セルリチウムイオン電池用温度保護機能付きハイサイド保護IC「NB7120シリーズ」を発売する。 OKIエンジニアリングが計測試験装置の校正作業を代行するサービスをリリース

OKIエンジニアリングが計測試験装置の校正作業を代行するサービスをリリース

OKIエンジニアリングは、計測試験装置の校正作業を代行するサービスとして「計測試験装置メーカーとのタイアップ校正サービス」を2024年6月26日にリリースする。 外観検査を効率化するMLA技術や多種AMRの一括制御技術など、OKIが新技術を公開

外観検査を効率化するMLA技術や多種AMRの一括制御技術など、OKIが新技術を公開

OKIは、技術開発拠点であるOKI蕨システムセンター(埼玉県蕨市)で、研究開発中の先端技術や取り組みを紹介する「OKI OPEN LAB 2024」を開催した。 OKIエンジニアリングが高分子材料の劣化評価サービスに熱老化試験と硬度測定を追加

OKIエンジニアリングが高分子材料の劣化評価サービスに熱老化試験と硬度測定を追加

OKIエンジニアリングは、高分子材料の劣化を化学的および物理的に評価する「高分子材料の劣化評価サービス」に熱老化試験と硬度測定を2024年6月12日に追加する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

素材/化学の記事ランキング

- 核融合による実用発電を目指す計画の公式パートナー制度、その狙いを考える

- 「日本にもうひとつ太陽をつくる」計画の第1弾公式パートナーが決定

- 気液間の物質移動、ガス吸収の考え方

- 100%植物原料由来のPEFフィルムを開発、高い剛性とガスバリア性を達成

- 【クイズ】国内の「錘」の減少率とは?

- 新入社員に読んで欲しい鉄鋼材料の基礎知識まとめ(Part1)

- 世界初のフッ素フリーネガ型ArF液浸レジスト、AI半導体向け先端ノードに対応

- 日本ゼオンが単層カーボンナノチューブ生産能力を数十倍へ、電池需要急増

- 千葉で油化ケミカルリサイクル設備の商業運転開始、使用済みプラを再資源化

- レゾナックがクロロプレンゴムを1kg当たり80円以上値上げ

コーナーリンク