三菱電機がSBD内蔵SiC-MOSFETのサージ電流集中の原因を解明、新チップ構造で克服:組み込み開発ニュース(2/2 ページ)

チップ面積全体の1%以下にSBDを内蔵しないユニットセルを作り込み

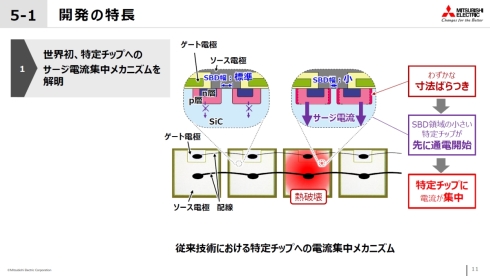

今回の開発成果では、SBD内蔵SiC-MOSFETを用いたフルSiCパワーモジュールにおいてサージ電流耐量を高められない、特定チップへのサージ電流集中メカニズムを世界で初めて解明した。物理分析とデバイスシミュレーションによる解析の結果から、内蔵されたSBDのわずかな寸法のばらつきが原因となって、SBD幅が0.1μm程度小さい特定のチップにのみ先にサージ電流の通電を開始してしまい、その結果として特定のチップにサージ電流が集中していた。

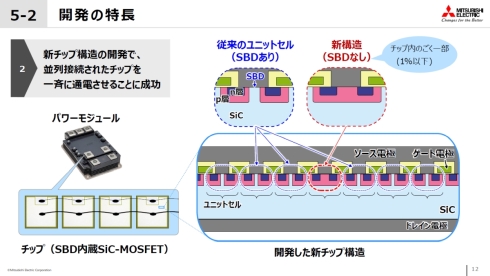

この原因となる寸法のばらつきは極めて軽微であり、製造上避けることは難しい。そこで、この問題の解決法として導入したのが新たなチップ構造である。SiC-MOSFETの間にSBDが内蔵されている素子構造単位を1つのユニットセルとして、チップ面積全体の1%以下のユニットセルをSBDを内蔵しない構造に作り込むようにした。SBDを内蔵しないユニットセルは、SBDを内蔵する他のユニットセルと比べて早くサージ電流の通電が生じるものの、SBDが存在しないため寸法のばらつきの影響を受けずサージ電流の集中が起こらず、全てのSBDを内蔵しないユニットセルで一斉にサージ電流の通電が始まる。

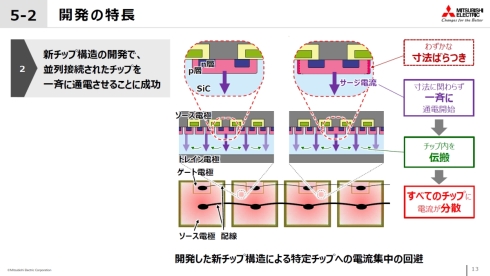

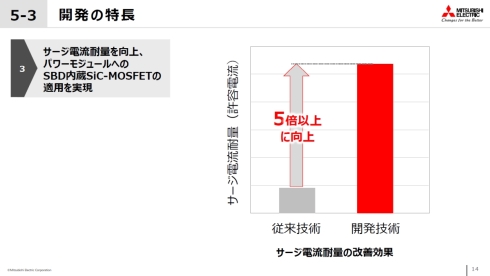

また、サージ電流は基板材料である周囲のSiCの抵抗を低減する働きがあるため、サージ電流の通電が生じたユニットセルの周囲でも、サージ電流の通電が連鎖的に引き起こされる。この現象により、SBDを内蔵しないユニットセルを起点としたサージ電流の通電がチップ全域に伝搬し、フルSiCパワーモジュールを構成するSBD内蔵SiC-MOSFETの全ての領域にサージ電流を分散させられるようになった。結果として、これまで課題になっていた特定チップへのサージ電流の集中によるチップの熱破壊を防ぐともともに、サージ電流耐量の大幅な増大につなげられたという。

なお、サージ電流の通電を連鎖的に伝搬する効果のために作り込んだSBDを内蔵しないユニットセルはチップ面積全体の1%以下にとどまるため、内蔵SBDの面積が減ることによるオン抵抗やスイッチング損失といったパワーモジュールの特性への影響はない。

関連記事

三菱電機のパワーデバイス事業は2030年度にSiC比率30%へ、鍵はモジュール技術

三菱電機のパワーデバイス事業は2030年度にSiC比率30%へ、鍵はモジュール技術

三菱電機が重点成長事業の一つであるパワーデバイス事業を含めた半導体・デバイス事業の戦略について説明。SiCモジュールをEV向けに展開するなどして、2030年度のパワーデバイス事業におけるSiC関連の売上高比率を30%以上に高めたい考えだ。 自動車と民生に注力する三菱電機のパワーデバイス事業、12インチ化も着々

自動車と民生に注力する三菱電機のパワーデバイス事業、12インチ化も着々

三菱電機が2021〜2025年度の中期経営計画で重点成長事業の一つに位置付けたパワーデバイス事業の戦略を説明。産業、再エネ、電鉄などの分野をベースロードとしながら、今後は自動車と民生の分野に注力し、2020年度の売上高1480億円、営業利益率0.5%から、2025年度に売上高2400億円以上、営業利益率10%以上に引き上げる方針だ。 直流配電で変換ロスを削減、三菱電機がSiC採用のDCマルチ電圧システムを開発

直流配電で変換ロスを削減、三菱電機がSiC採用のDCマルチ電圧システムを開発

三菱電機は2022年11月17日、SiCパワー半導体素子を採用し高い電力変換効率を実現した「DCマルチ電圧システム」を開発したと発表した。直流と交流の変換ロスを削減する直流配電システムの実現を目指し、同年11月18日から三菱電機のZEB関連技術実証棟「SUSTIE」での実証を行っている。 SiCパワー半導体の回路シミュレーションを高精度化、三菱電機から新SPICEモデル

SiCパワー半導体の回路シミュレーションを高精度化、三菱電機から新SPICEモデル

三菱電機は2020年7月9日、同社が開発したSiCパワー半導体「SiC-MOSFET」のスイッチング速度を高精度でシミュレーション可能な独自のSPICE(Simulation Program with Integrated Circuit Emphasis)モデルを新開発したと発表した。実測とほぼ同等のシミュレーションが可能となり、SiC-MOSFETを搭載したパワーエレクトロニクス機器の回路設計作業を効率化できる、 三菱電機から「世界最高レベル」のトレンチ型SiC-MOSFET、信頼性と量産性も確保

三菱電機から「世界最高レベル」のトレンチ型SiC-MOSFET、信頼性と量産性も確保

三菱電機は、1500V以上の耐圧性能と、「世界最高レベル」(同社)の素子抵抗率となる1cm2当たり1.84mΩを両立するトレンチ型SiC-MOSFETを開発した。家電や産業用機器、自動車などに用いられるパワーエレクトロニクス機器の小型化や省エネ化に貢献する技術として、2021年度以降の実用化を目指す。 HEV用SiCインバーターの体積がさらに半減、非対称構造でモーター出力密度を向上

HEV用SiCインバーターの体積がさらに半減、非対称構造でモーター出力密度を向上

三菱電機は、世界最高の電力密度を持つハイブリッド車(HEV)用パワーユニットと、世界最高クラスとする出力密度のモーターを開発した。パワーユニットは2024年度以降、モーターは2020年度以降の事業化を目指す。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク