先端ロジック/メモリチップのパターニングには計測技術のブレークスルーが必要:アプライド マテリアルズ ブログ(2/2 ページ)

3Dデバイス構造も、問題をさらに複雑にしている。平面デバイスに比べて計測回数が3倍多くなるからだ。高さのある構造になるため、局所でも層間でもひずみが生じやすい。次世代のgate-all-around(GAA)トランジスタではさらに多くの計測回数が必要となる。

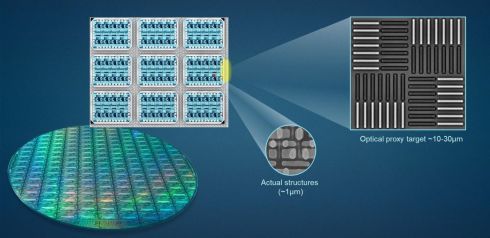

現在ファブでオーバーレイの制御に用いられている光学的計測装置は、実は製造されるデバイスの計測に求められる解像度を備えていない、と聞くと、経験豊富な業界ウォッチャーでも驚くかもしれない。実はこうした光学計測装置は、代替ターゲット(ダイの近傍に付けられた縦横の目印)を使ってパターンの位置の正しさを近似的に割り出しているのだ(図2)。

図2 今日の光学計測装置は代替ターゲットに依存している。パターンが正しく配置されているかどうかを見極めるために使われるこのターゲットは、ダイ上にある実際のフィーチャーより約10倍大きい[クリックで拡大]

図2 今日の光学計測装置は代替ターゲットに依存している。パターンが正しく配置されているかどうかを見極めるために使われるこのターゲットは、ダイ上にある実際のフィーチャーより約10倍大きい[クリックで拡大]この間接的な計測方法は、2Dスケーリング、単層成膜、エッチパターニングが主流だった時代に開発されたものである。プロセスエンジニアはオンデバイス計測の欠如をアルゴリズムで補ってきたが、この技法の精度は限界に達しつつある。しかも最近ではアライメントのわずかなエラーも許されなくなっている。

プロセスの量産化を加速するとともにプロセス制御によってエクスカーション(変動)を回避する上で、計測技術は極めて重要な役割を果たす。パターニングエラーが起きるとウエハー廃棄や低歩留まりにつながるのみならず、不良品ではないが性能や消費電力効率が悪いチップであるために安価でしか売れないなど、コスト面での影響が大きい。

こうした問題の解決は誰もが望むところだが、計測できない問題は解決できないし、見えないものは計測できない。

解決に向けて

パターニング制御を改善する1つの方法は、ターゲットベースの近似をやめて、ウエハー全面に配置された各ダイの状態を実測することである。

この理想的なアプローチはオーバーレイの問題を解決するのみならず、成膜、エッチング、熱処理、CMPなど、関連する全プロセス技術で問題点の診断に利用可能なデータをもたらす。ウエハー全面にわたって膨大な数のサンプリングが可能になれば、プロセスエンジニアはプロセスのばらつきをより迅速に検出して解決でき、PPAC(消費電力、性能、面積当たりコスト)の改善とt(歩留まり確保までの期間)の加速が可能となる。さらにこうしたデータをアプライド マテリアルズの画期的なAIxプラットフォームなどのAIエンジンに投入すれば、新しい材料やプロセス技術の開発と商用化のスピードアップにつながるだろう。

関連記事

- ≫連載「アプライド マテリアルズ ブログ」のバックナンバー

第4のコンピューティング時代に求められるのは先端ロジック・メモリチップだけではない

第4のコンピューティング時代に求められるのは先端ロジック・メモリチップだけではない

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、同社のMaster Classイベントで発表されたヘテロジニアスデザインと先進のパッケージング技術についてさらに掘り下げる。 ヘテロジニアスデザインと先進的パッケージングがPPACtを改善

ヘテロジニアスデザインと先進的パッケージングがPPACtを改善

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、同社のMaster Classイベントで発表されたヘテロジニアスデザインと先進のパッケージング技術について紹介する。 半導体イノベーションを支えるのは先端技術だけではない

半導体イノベーションを支えるのは先端技術だけではない

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、同社のMaster Classイベントの開催と絡めて、ICAPS(IoT、通信、自動車、パワー、センサー)分野の動向について紹介する。 新規ファブのサステナブル化に向けた主要半導体メーカーの動き

新規ファブのサステナブル化に向けた主要半導体メーカーの動き

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、半導体ファブの省エネや脱炭素の実現に向けた取り組みを紹介する。 シリコンカーバイド(SiC)が電気自動車の普及に拍車

シリコンカーバイド(SiC)が電気自動車の普及に拍車

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回のテーマは電気自動車への搭載が進むSiCデバイスだ。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

コーナーリンク