先端ロジック/メモリチップのパターニングには計測技術のブレークスルーが必要:アプライド マテリアルズ ブログ(1/2 ページ)

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、半導体の微細化が進展する中で求められている計測技術のブレークスルーについて紹介する。

本記事は「Applied Materials Blog」の抄訳です。

企業経営では「測れるものは改善できる」という格言がある。データが容易に入手でき、一貫性があるなら、計量学(計量・計測などを科学的に研究する学問)は確かに有効だ。しかし半導体の世界では、いつもそうした条件がそろうわけではない。測ろうとする対象が大きく変化して計測が意味を成さなくなってしまう場合もあれば、原因不明の歩留まり低下が起きてはじめて計測技術の不備が判明するケースもある。業界では、今まさにこれが大きな問題になっている。

半導体製造は巨額の費用がかかる極めて複雑な事業だ。研究開発から量産までの道のりは、競争の連続といってよい。最初にゴールインすれば、売り上げ、市場占有率、利益率のあらゆる面で優位に立てる。半導体製造プロセスを制御し完成に導く上で、計測技術は常に重要な役割を果たしてきた。しかしチップ構造が極めて微細かつ複雑になった今では、計測方法そのものを進化させる必要が生じている。

岐路に立つパターニング制御

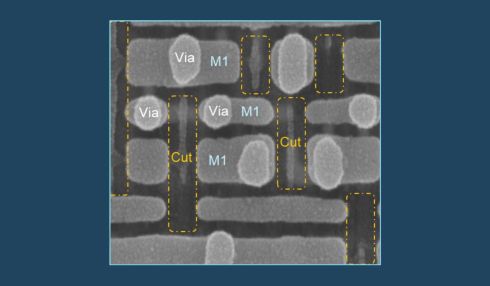

先進的なチップは1層ずつ構築され、各層には数十億個もの微細なフィーチャーが正しく整然とパターン化されて、最高の性能と電気特性を持つ実用的なトランジスタや配線が形成される。パターニングのエラーは市場投入の遅れや歩留まり低下をもたらし、ひいては半導体に支えられる経済の停滞を招きかねない(図1)。

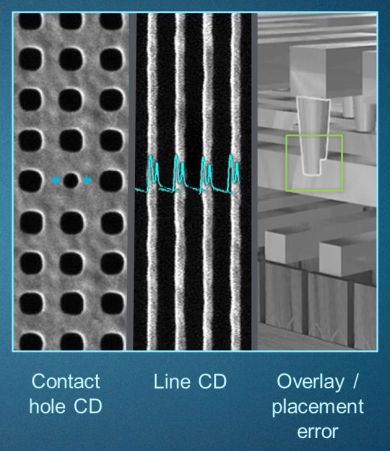

半導体業界ではシンプルな2次元(2D)チップデザインからマルチパターニングやEUV(極端紫外光)に基づく複雑な3次元(3D)デザインへの移行が進み、パターニング制御は転換点を迎えている。半導体業界が従来アライメント計測に利用してきた光学的オーバーレイツールその他の技法では、もはや今日の最先端ロジックやメモリに要求される精度を確保できない。

チップ上の各層を極めて高精度で位置合わせする工程は、プロセスチャンバー内の部位によってプロセス条件にばらつきがあるため、さらに困難の度合いが増す。つまりダイがウエハー上のどの位置にあるかによって、形成されるパターンが微妙に変わりかねないのだ。従って、各層を上下の層と完璧に位置合わせするのみならず、ウエハー全面にわたって位置合わせを均一に保たないと、ウエハーの部位によってデバイスの歩留まりや電気特性に影響が出る恐れがある。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

コーナーリンク