ローエンドのFPGAがドライバー監視や電子ミラーを実現、消費電力4.6Wで深層学習も:オートモーティブワールド 2017

ザイリンクスは「オートモーティブワールド2017」において、ローエンドの同社FPGAを使用した高度運転支援システムのデモンストレーションを行った。「高コストなASICの納入を待たなくても、FPGAの1チップで実現できることは多い」(ザイリンクス)ということをアピールした。

ザイリンクスは「オートモーティブワールド2017」(2017年1月18〜20日、東京ビッグサイト)内の「第9回 国際カーエレクトロニクス技術展」において、ローエンドの同社FPGAを使用した高度運転支援システムのデモンストレーションを行った。「高コストなASICの納入を待たなくても、FPGAの1チップで実現できることは多い」(ザイリンクス)ということをアピールした。

ローエンドFPGA、いろいろできる

28nmプロセスを用いたローエンドのFPGA「Zynq-7000 All Programmable SoC」(Zynq-7020)を使って、ドライバーモニタリングシステム、従来のミラーをカメラとディスプレイで置き換える電子ミラー、サラウンドビュー、データ伝送と電力伝送を同時に行うPoE(Power over Ethernet)を実演した。

ドライバーモニタリングシステムはFovioと共同で開発したもの。赤外線カメラでドライバーのまぶたの動きや目線、頭部の向きや傾きをリアルタイムに検知する。デモでは、ドライバーが濃い色のサングラスをかけたりマスクを着用したりしても正確に検出。マスクを着用の上、片目を隠しても正確に視線の向きを検知できた。ドライバーの動きを検出するソフトウェアとカメラの両方を1チップで動作できる点が特徴だという。

ザイリンクスは2018年にドライバーモニタリングシステムが各国で義務化されると見込んでおり、FPGAによる低コストなシステムが不可欠だとしている。

電子ミラーは、サイドミラーとルームミラーを代替することを想定し、フルHDカメラ3つを用いた。明暗が大きい環境向けの白とびや黒つぶれの補正や、夜間の表示向けに物体の輪郭を強調する表示といった画像処理をZynq-7020で行う。「車両のナンバーなどを従来のミラー並みに視認するにはフルHDと60fpsは最低限必要だが、ローエンドのFPGAで処理することができる」(ザイリンクス)。

電子ミラー用のカメラが撮影した映像をドライブレコーダーに記録、復元するデモも行った。記録媒体は振動に弱いHDDではなく、SSDディスクを選んだ。ただ、映像は圧縮して保存する上に、SSDディスクは高温下での読み込みに課題がある。単純に再生するだけでは画像にノイズが入り、車両のナンバーなど細部までは復元できない。デモでは、シグリードの強化型ECC(誤り検出訂正)を組み合わせて、ドライブレコーダーに記録した映像の信頼性を確保した様子も紹介した。この強化型ECCもZynq-7020に実装できるという。

PoEのデモでは、Zynq-7020をベースにした複数のカメラモジュールのフュージョンを紹介した。遅延なく同期し、物体検出やゆがみ補正も実現。改ざん対策として、デバイスごとに固有のアドレスの認証も行う。サラウンドビューは、広角カメラの高画質な映像をシームレスに合成し、視点を真上以外にも自由に切り替えられるようにした。

歩行者検知は16nmのFPGA、消費電力は4.6W

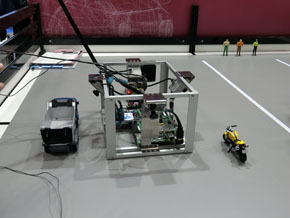

前回の国際カーエレクトロニクス技術展でザイリンクスは、16nmプロセスを適用した最新のプログラマブルSoC「Zynq UltraScale+ MPSoC」の動作デモを披露した。今回は、同じ製品でディープラーニング(深層学習)による歩行者検知のデモを行った。

歩行者がどこにいるかを検知、追跡するセマンティック セグメンテーションは、MPSoCに搭載されている合計4つのARMプロセッサ、画像表示用のGPU、ネットワークを実装しているプログラムロジック部の消費電力を合算して4.6Wで動作した。

デモでは使用していないプロセッサをオフにするような最適化は行っておらず、より少ない消費電力でも動作できるという。さらにFPGAブロックの規模が小さい品種では、3W以下にも消費電力を抑えられるとしている。

関連記事

運転支援システムの開発、ASICにする? FPGAにする?

運転支援システムの開発、ASICにする? FPGAにする?

FPGA大手のザイリンクスが記者向けに勉強会を実施し、先進運転支援システム(ADAS)でFPGAを使うメリットを解説した。車両や歩行者、白線などを認識する処理は、FPGAの得意分野だという。コストや性能の面からも、FPGAはADASで強みを発揮しそうだ。 ザイリンクスの16nm世代プログラマブルSoC、消費電力5W以下を実現

ザイリンクスの16nm世代プログラマブルSoC、消費電力5W以下を実現

ザイリンクスは、「オートモーティブワールド2016」において、16nmプロセスを適用した最新のプログラマブルSoC「Zynq UltraScale+ MPSoC」の動作デモを披露。4コアの「Cortex-A53」やFPGAブロックなどを動作させても、車載情報機器のSoCに求められる5W以下の消費電力になることを示した。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部) 産業用IoTの本命か、FPGAはエッジコンピューティングの勝利者となる?

産業用IoTの本命か、FPGAはエッジコンピューティングの勝利者となる?

インダストリー4.0や産業用IoTなど製造現場のIoT活用が活発化している。その実現のカギを握る要素の1つがエッジコンピューティングである。FPGA大手のザイリンクスは「エッジコンピューティングにFPGAは最適だ」と主張し、産業用IoTへの提案を強化する。

Copyright © ITmedia, Inc. All Rights Reserved.

モビリティの記事ランキング

- 「EVはオワコン」なのか? 消費者の半数がガソリン車を選択、専門家の見解は

- ジヤトコのドライブユニット「GLIDE AXCEL」を搭載した電動アシスト自転車が誕生

- ヒューマノイドの“始祖”ホンダP2――「不可能」に挑んだ自立二足歩行の歩み

- トヨタが研究開発拠点「TTC-S」を公開、「走る・壊す・直す」を一気通貫で行う

- ホンダの小型EV「Super-ONE」は日常の移動に刺激を与える 2026年5月下旬に販売へ

- 欧州に迫り来るPHEV淘汰の危機

- デンソーとロームの協業は「新たなステージ」へ、株式取得提案は取り下げ

- 小型船舶でも進む操船のシステム化、環境対応も浸透――ボートショー2026レポート

- トヨタは中東情勢影響で6700億円の減益見通し、稼ぐ力の強化やロボティクスで対抗

- 中東情勢が国内製造業に与える減益影響じわり、日立200億円デンソー450億円

コーナーリンク