SoC設計者がIPに関心を持つべきタイミング:SYSTEM DESIGN JOURNAL(3/4 ページ)

IoTへ

IoTアプリケーションに自動車業界での信頼性や安全性規格のようなものが求められることはありませんが、IPに関する問題を明らかにする独自の方法を持つでしょう。多くのIoTアプリケーションは、動作する消費電力に厳しい制約を設けているからです。

IoTの外側境界に近づくほど、エネルギーへのアクセスが減少します。電源アダプターは小型バッテリーに、バッテリーはエネルギースカベンジングになり、省エネへの配慮は強迫観念になります。回路デザインの基本ルールが変わり始める0.5〜0.4Vのしきい値の範囲でさえ、低電圧動作が当然です。

設計者が、動作のわずかなバーストによって時々中断するゼロに近い消費電力での長い休止時間を目標にするにつれ、デューティサイクルが長くなります。これらの方策の全てがIPに関するSoC開発者の決定に影響を及ぼします。

オートモーティブグレードの信頼性追求と同様、新しい各種超低電圧プロセスとライブラリを使用した低電圧動作がファウンドリで追求され始めています。カンファレンスでは、Global foundriesのデザイン・エンジニアリング担当ディレクターであるGerd Teepe氏が、完全空乏型シリコンオンインシュレータ(FDSoI)22nmプロセスの調整可能なボディーバイアスを使用して、性能損失を最小化した0.4V動作を達成する取り組みについて説明しました。Teepe氏の論文によると、0.4V電源の22nmFDSoIデバイスは標準電圧チップのわずか8%の消費電力で動作します。

この範囲でFDSoIチップを動作させるには、大きなボディーバイアスだけでなく新しいセルライブラリも必要になります。これらの変化については、TSMCのテクニカルマネージャーであるMarco Vrouwe氏が同社の新しい16nm小型FinFET(ffc)プロセスを0.4V動作にするプログラムについて説明した、別の論文でさらに明らかになりました。

Vrouwe氏によれば幾つかの要因が関係します。1つはしきい値に極めて近い電圧により電源電圧変動とプロセス変動の影響がいずれも増幅されることです。もう1つは、この範囲ではプロセス変動の配分がゆがむため、タイミングツールのアルゴリズムを変更する必要があることです。

最後にVrouwe氏は、TSMCの16個のffcライブラリである種の選別を行う必要があったとも述べています。0.4Vで問題なく動作するセルもあれば、再設計によって許容変動範囲を拡大する必要があるセルもあり、感度を下げることができないため、低電圧ライブラリから削除したセルもあったそうです。

新しいライブラリとプロセスコーナーがSoC開発者に初歩的な質問を投げかけます。SoC開発者は、新しい環境で既存IPを使用して0.4Vで動作する回路にそれが実際に合成されるのを期待するだけなのか、新しいプロセスと電圧でのシリコン検証を要求するのかという質問です。チップ開発者がどちらを選ぶかは、システム設計者にとって非常に重要な意味があります。

省エネに対する要求はIP統合にも影響を及ぼします。ブロックが低電圧で動作すると電源レールでのIRドロップに対する感度が大幅に上がり、基板結合に対する感度も上がる可能性があります。ここでの問題は通常のIP検証では検出されません。SilabtechのChakravarty氏によれば、IPブロック外部のその他の決定も、特にハードIPで障害を引き起こすことがあります。低デューティ・サイクルデザインにあるような、パワーゲートブロックでの電源レールのスイッチングトランジスタは既存のIPと連動するでしょうか。I/Oピンへのマルチプレクサについてはどうでしょうか。

関連記事

人工知能の奇跡的な復権

人工知能の奇跡的な復権

囲碁王者への勝利を果たすなどAI(人工知能)への注目は依然として高くありますが、研究史を知る身からすれば、AIへの興奮はジェットコースターのようなものであるとも感じられます。多岐にわたる成果を挙げ始めた現代のAIは何が違うのでしょうか。 中世史に学ぶ、組み込みシステムのセキュリティモデル

中世史に学ぶ、組み込みシステムのセキュリティモデル

セキュリティの確保は重要ですが、リソースや利便性との兼ね合いも求められます。組み込みシステムのセキュリティ確保について、中世の城の防衛策を例に考察します。 WoT(Web of Things)と化すIoTに待ち受ける、分断された未来

WoT(Web of Things)と化すIoTに待ち受ける、分断された未来

さまざまな企業や勢力がIoTを目指していますが、残念ながら勢力ごとの対話はほぼ存在していません。Web技術を共通言語とし、IoTを「WoT(Web of Things)」とすることで妥協点を見いだそうという動きはありますが、成功するかは不透明と言わざるを得ません。 「SoC」or「SoC」?統合へのさまざまな道

「SoC」or「SoC」?統合へのさまざまな道

1つのダイに複数機能を実装するSoC(System on Chip)化の波は高まるばかりです。アーキテクトはダイ間接続とマルチダイパッケージングの動向に注意を払い、コストや消費電力、将来性までも視野に入れた選択をしなければなりません。 組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。 FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

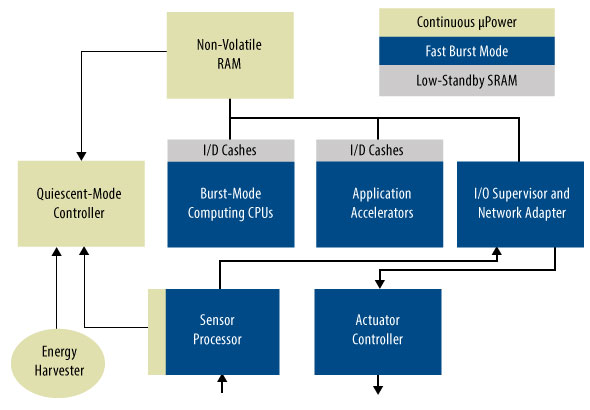

図2. SoCはIoTの境界に新しい種類のブロックを必要とする場合があります

図2. SoCはIoTの境界に新しい種類のブロックを必要とする場合があります