FPGAコンパイルを最大8倍高速化、「Quartus II」に新エンジン:FPGA

アルテラがFPGA開発環境「Quartus II」の最新版と最新版に対応する階層型データベース生成エンジン「Spectra-Q エンジン」を発表した。導入によってコンパイルを最大8倍高速化するとしている。

米Alteraは2015年5月11日(現地時間)、同社の提供するFPGA/SoC開発環境「Quartus II」の最新版「v 15.0」と新バージョンに対応する階層型データベース生成エンジン「Spectra-Q エンジン」を発表した。v 15.0は既に提供開始されており、Spectra-Q エンジンはアーリーアクセスプログラムに参加することで利用できる。

このSpectra-Q エンジンはSoC FPGA「Stratix 10 SoC」および「Arria 10 SoC」に向けたもので、最大で8倍というコンパイルの高速化と、最大10分の1というイタレーション数の削減が可能となることから、同社ではプログラマブルデバイスの設計効率向上と市場投入時間の短縮を可能にするとしている。

プログラマブルロジックデバイスにおいては近年、数百万のロジックエレメント(ロジックセル)を実装するものも珍しくなく、複雑化の一途をたどっている。また、開発時間短縮の要望も高く、設計者のバックグランドも多様化している。Spectra-Q エンジンはQuartus IIの中核技術として開発されたもので、 論理合成/配置配線/タイミング解析アルゴリズムを備えており、コンパイルの各ステージで高精度な制御が行え、また、各ステージでの再エントリとインクリメンタルな最適化も行える。

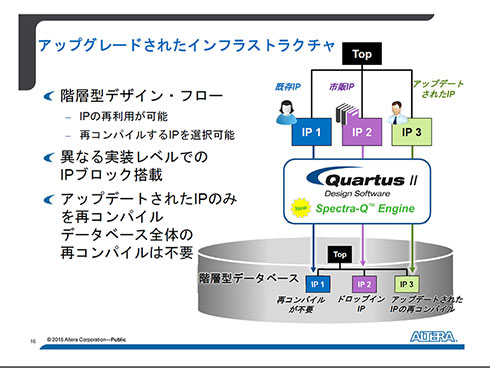

階層型フローを採用することによって、アップグレードされたIPだけをコンパイルすることもできる他、データベース全体の再コンパイルを行う必要がないため、手戻りを最小限に抑えての開発が行える。コンパイルエンジンそのものも改良されており既存製品に比べて最適化が進んでいる他、多数のコンピュータ/ノードに処理を分散しての高速化にも対応している。開発環境の柔軟さも備えており、HDLに加えてC/C++からIPコアを開発できる「HLS用A++コンパイラ」もサポートしている。

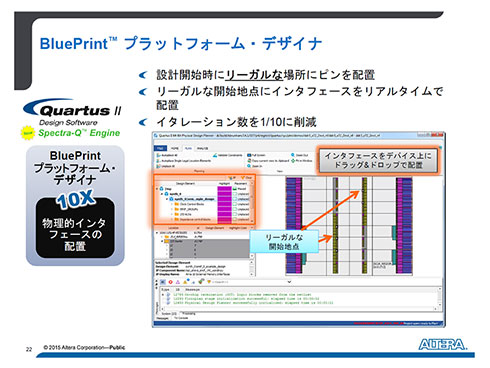

また、Spectra-Q エンジンをベースに開発されたプラットフォームデザインツール「BluePrint Platform Designer」ではデバイスの適切な位置に物理的デバイスをドラッグ&ドロップで配置が行え、イタレーション数を10分の1に削減するとしている。

関連記事

「MAX 10 FPGA」で極薄パッケージを実現する新技術

「MAX 10 FPGA」で極薄パッケージを実現する新技術

TSMCとアルテラは「MAX 10 FPGA」向けに、0.5mm以下(はんだボールを含む)の薄型パッケージを実現する新技術を共同開発した。 アルテラ、浮動小数点DSPサポートの「Quartus II 開発ソフトウェア v14.1」

アルテラ、浮動小数点DSPサポートの「Quartus II 開発ソフトウェア v14.1」

アルテラは開発ツール「Quartus II 開発ソフトウェア v14.1」を発表した。「Arria 10 SoC」が実装する浮動小数点DSPブロックをサポートしており、最大1.5TFLOPSのDSP性能を得ることが可能になる。 日本市場については「満足」、米アルテラ幹部が語るSoC FPGA事業の近況

日本市場については「満足」、米アルテラ幹部が語るSoC FPGA事業の近況

「Cyclone V SoC」で2012年よりSoC FPAGの供給を開始したアルテラ。わずか2年足らずではあるが、日本国内においても多くの企業に利用されている。14nmプロセス「Stratix 10」のテープアウトを控えるが、サポートや周辺環境の整備にも注力する考えだ。 アルテラ、コンパイルを高速化した「Quartus II Arria 10」新バージョン

アルテラ、コンパイルを高速化した「Quartus II Arria 10」新バージョン

アルテラは20nm FPGA/SoC用の開発ソフト「Quartus II 開発ソフトウェア Arria 10 エディション v14.0」を発表した。競合する他社20nmツールに比べ、平均2倍以上のコンパイル速度を実現するという。 2つのフラッシュメモリを集積、アルテラが「MAX 10 FPGA」を発表

2つのフラッシュメモリを集積、アルテラが「MAX 10 FPGA」を発表

アルテラは、「Generation 10」製品群として、新たに「MAX 10 FPGA」を発表した。新製品は、2つのコンフィギュレーション用フラッシュメモリブロックやソフトコア「Nios II」プロセッサなどを搭載している。周辺機能を集積することで、同等性能のFPGAに比べて、ボード占有面積を最大50%も節減できるという。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク