1チップに1兆個のトランジスタ集積に向け、インテルが次世代半導体製造技術を発表:組み込み開発ニュース

インテルの半導体製造部門であるIntel Foundryは「第70回 IEDM 2024」において、同社で開発中の次世代半導体製造技術を発表した。半導体業界が、2030年までに1兆個のトランジスタを半導体上に集積することを目指す中で、今後10年間のブレークスルーを支える技術になるとする。

インテル(Intel)の半導体製造部門であるIntel Foundryは2024年12月7日(現地時間)、米国サンフランシスコで開催されている半導体/電子デバイスの国際会議「第70回 IEDM(International Electron Devices Meeting) 2024」(同月7〜11日)において、同社で開発中の次世代半導体製造技術を発表した。半導体業界が、2030年までに1兆個のトランジスタを半導体上に集積することを目指す中で、今後10年間のブレークスルーを支える技術になるとする。

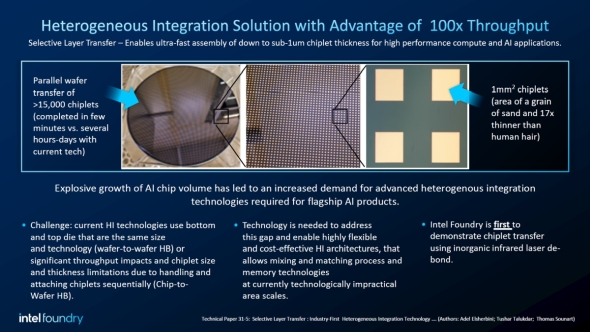

今回発表した技術は、先進パッケージング、トランジスタ、配線層の3分野から成る。先進パッケージングで発表したのは、さまざまな半導体のダイをパッケージ内に集積する上で重要な役割を果たすチップレット技術であるSLT(Selective Layer Transfer)だ。従来は、同じサイズとプロセス技術で半導体のダイを作り込んだ2枚のウエハーを重ねて2個のダイの積み重ねを作る「wafer-to-wafer HB(Heterogeneous Bonding)」や、半導体ダイを1個ずつウエハー側のダイと組み合わせる「Chip-to-Wafer HB」が一般的だった。無機赤外線レーザーを用いて行うSLTは、厚さ1μm以下の半導体ダイと半導体ダイの接合を従来比で100倍以上のスループットで行えるという。

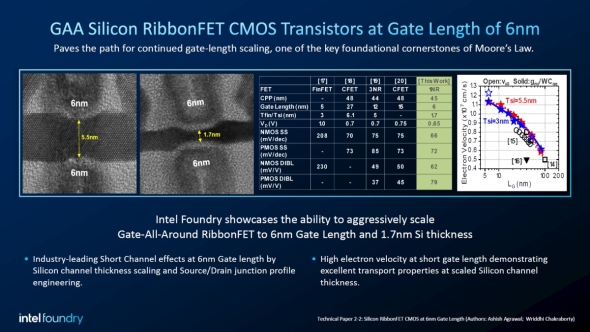

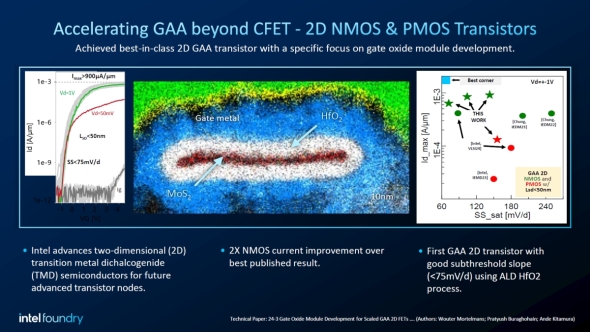

トランジスタでは、2nmプロセス以降での採用が想定されているGAA(Gate All Around)トランジスタの1種であるシリコンRibbonFETについて、6nmのゲート長に対して、チャネル厚さを1.7nmまで薄くすることに成功した。また、GAAにおいてPMOSとNMOSを垂直方向に積層するCFET(Complementary FET)以降の技術として想定されている2Dトランジスタ向けでは、TMD(遷移金属ジカルコゲナイド)とHfO2(酸化ハフニウム)を用いたゲート長30nmのトランジスタを作成し、良好な特性が得られているという。

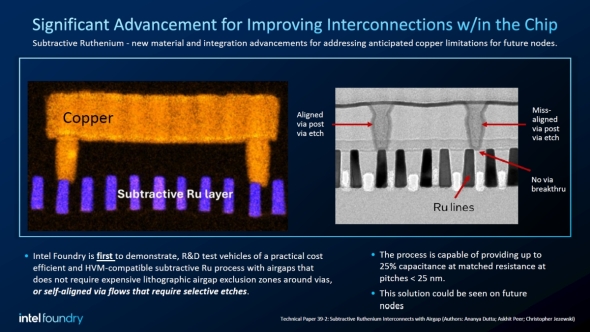

配線層では、ルテニウムを用いた配線層に薄膜抵抗とエアギャップを組み合わせるサブトラクティブルテニウム(Subtractive Ruthenium)を発表した。この技術は、ルテニウム配線のビアを作り込むのに高価なリソグラフィーや選択的エッチングなどのプロセスを必要としない。また、配線層のピッチが25nm以下の場合、配線層間静電容量を25%削減できるという。

関連記事

インテルが「4年で5つのプロセスノード実現」にめど、Intel 7からIntel 18Aまで

インテルが「4年で5つのプロセスノード実現」にめど、Intel 7からIntel 18Aまで

インテルは、2023年12月14日に米国本社が発表した新製品「Core Ultra」と「第5世代 Xeon SP」を紹介するとともに、2024年以降に予定している製造プロセスの立ち上げ時期や製品展開の方針などについて説明した。 インテルがガラス基板で半導体進化の限界を打ち破る、2020年代後半に量産適用

インテルがガラス基板で半導体進化の限界を打ち破る、2020年代後半に量産適用

インテルは、複数のチップレットを搭載する大規模半導体パッケージの進化に貢献するガラス基板技術の開発を進めるとともに、10億米ドル以上を投資して研究開発ラインを構築したことを明らかにした。 インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ

インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ

インテル日本法人が、米国本社が2021年7月26日(現地時間)にオンライン配信したWebキャスト「Intel Accelerated」で発表した先端半導体製造プロセスやパッケージング技術について説明した。 インテルの新たなフラグシップ「Lunar Lake」、次世代AI PCに向け大胆な設計変更

インテルの新たなフラグシップ「Lunar Lake」、次世代AI PCに向け大胆な設計変更

インテルは、2024年第3四半期の市場投入が予定されているクライアント向けプロセッサの新製品「Lunar Lake」(開発コード名)の技術詳細について説明した。 インテルがNVIDIA対抗のAIアクセラレータ「Gaudi 3」を発表、「Xeon 6」も投入

インテルがNVIDIA対抗のAIアクセラレータ「Gaudi 3」を発表、「Xeon 6」も投入

インテルは、顧客とパートナー向けのイベント「Intel Vision 2024」において、クラウド/データセンター向けAIアクセラレータ「Gaudi」の最新モデル「Gaudi 3」と、ワークステーション/サーバ向けプロセッサ「Xeon」の最新モデルとなる「Xeon 6」を発表した。 新生アルテラが再誕、インテルからの独立で「FPGAだけに専念できる」

新生アルテラが再誕、インテルからの独立で「FPGAだけに専念できる」

インテルでFPGA製品を手掛けるPSG(Programmable Solutions Group)が、インテルからのスピンアウトによりアルテラ(Altera)として独立することを発表した。2015年のアルテラ買収から約10年間を経て、再びアルテラが独立企業としてFPGA製品を展開して行くことになる。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

コーナーリンク