FPGA、DDRも怖くない! ロジアナによる簡単デバッグ:いまさら聞けないロジック・アナライザ入門(5)(1/2 ページ)

最終回は、ロジック・アナライザの用途として最近よく使用されているFPGAやDDRメモリのデバッグ解析例を紹介する

実機の環境はシミュレーションのように理想的ではない。実機で発生しているイベントをリアルタイムに観測できるツールはロジック・アナライザ(ロジアナ)だけだ。本稿では、これからロジアナを使ってみようと考えている読者を対象に、ロジアナの測定原理から、実機デバッグで役に立つテクニックまで順に解説していく。(編集部)

いままでロジック・アナライザについて、タイミング解析とステート解析の違い、MSOとの違い、プロービングの選択などのそれぞれの観点から解説してきました。大規模で多機能化するシステムに対して、仕様どおり動作していることをスマートに実機検証し、どのようにして早く不具合を発見していくのか? 最終回となる今回は、最近ロジック・アナライザの用途としてよく使用されているFPGA、DDRメモリのデバッグ解析例を紹介します。

FPGAアナライザを使用した実機デバッグ例

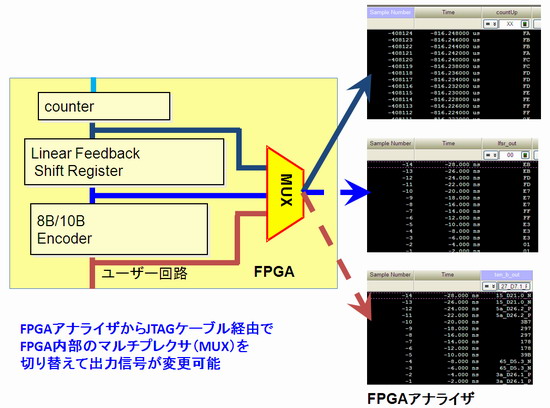

前回、FPGAアナライザは「FPGA内部にデバッグコアを入れてロジック・アナライザでFPGA内部を簡単にモニタできるツール」と紹介しました。図1は実際にFPGA内部のそれぞれのモジュールを観測した例を表します。この例ではFPGA内部からPCI ExpressやシリアルATAなどの外部I/Oへのデータを送るために、Linear Feedback Shift Registerでスクランブルを掛けて、8B10B回路にデコードするところまでをFPGA内部で行い、外部のユーザー回路のPHYにデータを送ることを想定しています。なおこの例では分かりやすいように、実際に送るデータの代わりにIncrement Counterを使用しています。

IPなどを使用して複雑な回路を組み込んだ場合、システムに不具合があったときにどこに問題があるのか切り分けることが重要になります。FPGAアナライザを使用するとFPGAを停止することなく出力する信号を変更することが可能なので、システムを動作させながらどの機能ブロックで不具合が起きているか簡単に確認することができます。さらにロジック・アナライザの豊富なトリガ機能が使用できることと、メモリ長も数メガサンプルから数百メガサンプルまであるので、実システムで長時間の動作を確認することが可能です。いかにシミュレーションが便利になっていても、実機で起きている問題は実機で観測した方が早いケースがあります。

FPGAアナライザを使用したFPGA外部信号との相関

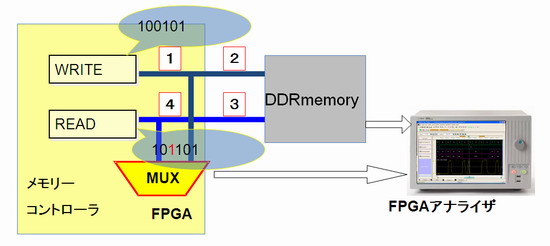

また、FPGAアナライザはロジック・アナライザをベースにしていますので、FPGA内部だけではなくボード上のほかの信号と併せて測定することも可能です。図2はFPGA内部の信号とボード上のDDRメモリの信号を同時に測定している例です。

例えばFPGAとDDR間のメモリ・アクセスに問題があった場合、FPGAの中だけ、もしくはボード上だけを個別に観測していても、なかなか解決はできません。このような問題は時間相関を取って、いつどこで障害が発生しているのか把握することが重要かつ必要です。メモリ・アクセス動作は次の4つに分けられます。

- FPGA内部のメモリ・コントローラからの書き込みの信号

- ボード上のDDRメモリへの書き込みの信号

- ボード上のDDRメモリからの読み出しの信号

- FPGA内部のメモリ・コントローラへの読み出しの信号

ロジック・アナライザのFPGAアナライザ機能とDDRアナライザ機能を併用すると簡単にFPGA内部の信号とボード上のDDRの信号と併せて測定することができます。例えば、FPGAアナライザで1と4のメモリ・コントローラの書き込み/読み出しアクセスをしながら、DDRアナライザで2と3のDDRメモリの書き込み/読み出しアクセスをデコードしてモニタすることが可能です。

さらに最近のロジック・アナライザには、1台でタイミング解析とステート解析を同時に行えるものもあり、FPGAで問題となりやすい外部からの非同期信号入力の動作確認を行うことも可能です。例えば3と4の読み出し動作の確認時に4の確認はFPGA内部のクロック信号に同期したステート測定を行い、3の部分はタイミング測定を使用してクロックとデータのタイミングの確認を同時に行うことも可能です。

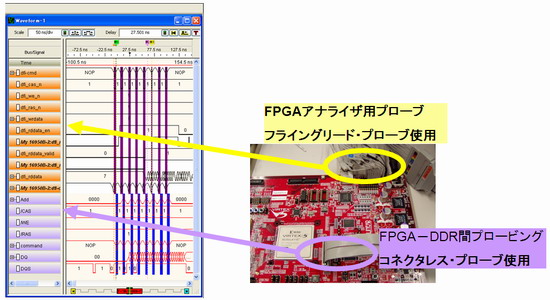

実際にFPGAアナライザを使用した測定例を図3に表します。

このボードでは、FPGAの内部信号用のプローブはフライングリード・プローブを使用して、FPGAとDDRメモリ間にはコネクタレス・プローブを使用しています。

ちなみに、このFPGAアナライザのようにFPGAの内部観測を行う機能は5年以上前からあったのですが、最近の高性能FPGAや既存のIPの使用比率の高まりとともにニーズが急増しています。特に既存のIPを使用した場合、サポートを受けるためにはIPに問題があることをユーザーが切り分けなければなりません。複雑なIPを開発するより既存のIPを利用することで開発工数を劇的に削減することができますが、その半面、デバッグの難易度も劇的に増加します。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

図1 FPGAアナライザ使用例(内部観測)

図1 FPGAアナライザ使用例(内部観測) 図2 FPGAアナライザ使用例(外部相関)

図2 FPGAアナライザ使用例(外部相関) 図3 FPGAアナライザ使用例(DDRメモリとの外部相関)

図3 FPGAアナライザ使用例(DDRメモリとの外部相関)