FPGA、DDRも怖くない! ロジアナによる簡単デバッグ:いまさら聞けないロジック・アナライザ入門(5)(2/2 ページ)

DDRアナライザ使用例(DDRメモリの初期化の確認)

DDR1まではICのパッケージによっては、何とかクリップでアドレス、コマンド各信号をプロービングしてロジック・アナライザで観測することが可能でしたが、DDR2からパッケージがBGAになったため、DDRメモリの動作確認を行ううえでプロービングをどうするかを検討しなければならず、以前はそれが最初のハードルになっていました。現在では第4回で紹介したBGAプローブがあるので、ロジック・アナライザで簡単にDDRメモリの動作検証ができます。

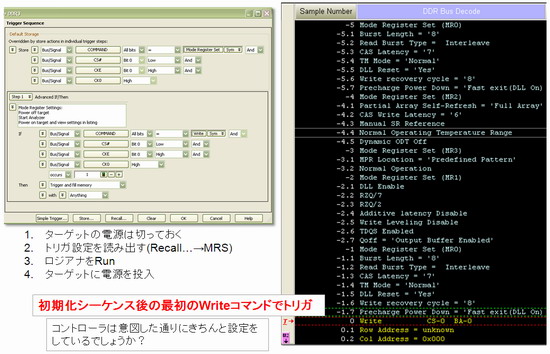

実際に、DDRメモリを使用するうえで最初に必要な動作検証として「コントローラからメモリの初期化」があります。実際の測定例を図4に表します。

DDRアナライザで初期化するレジスタアクセスをトリガにセットするだけで測定が行えます。デコード結果を仕様と比較すればよいので簡単に確認できます。見落としがちなところでもありますので、思い込みで“こうなっているはずだ”ではなく、実システムでも、きちんと仕様どおり設定されていることを確認することをお勧めします。

DDRアナライザ使用例(アクセスの確認例)

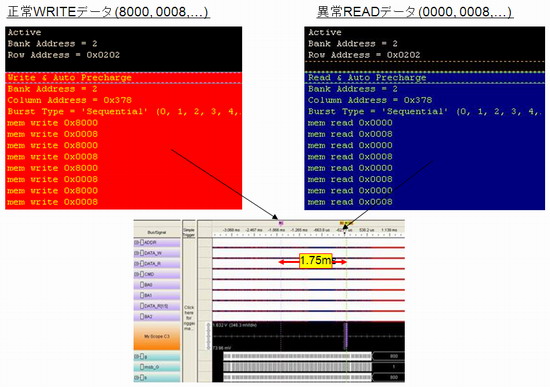

実際に書き込んだデータが読み出したデータと一致しないトラブル事例を図5、図6に表します。

FPGAアナライザでも紹介しましたが、まずは各動作を1つずつ確認することが重要になります。書き込んだデータ値と読み出したデータ値が異なる場合、読み出したアドレスに書き込んだときのデータが正しいかどうか確認する必要があります。ロジック・アナライザのメモリとストア条件を使用してReadとWriteイベント以外をフィルタ・アウトすることで、これらの間隔の空いたメモリ・アクセスも長時間のレコーディングが可能です。その結果、図5のとおり書き込んだデータは0x8000、0x0008の連続ですが、読み出したデータは0x0000、0x0008となっていることが分かります(図5)。

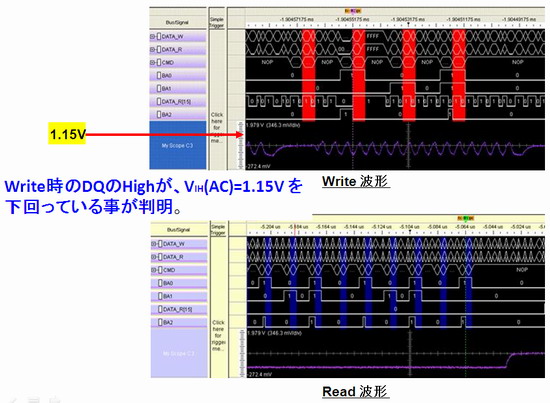

図6では、オシロスコープとロジック・アナライザの連携機能を利用して、実際にオシロスコープにて電圧を確認したところ、書き込み時の振幅が小さかったため、データを正しく書き込めていなかったことが確認できました。

このように実システムでのトラブルは物理層からソフトウェアまでさまざまなところに問題が潜んでいます。そのようなときでもロジック・アナライザはイベント検出器としてほかの測定器と連動させ、単体では難しい現象をスマートに確認することができます。さらにCPUやFPGAの内部信号を観測するだけでなく、外付けのメモリや周辺回路の信号などとも相関を取って、システム全体の動作を検証することが可能です。

最後に

ロジック・アナライザはその成り立ちからいまに至るまで、デジタル・デバッグのためのツールとして進化してきています。システムが日々複雑化しているにもかかわらず、オシロスコープとシミュレータだけでデバッグをしていないでしょうか?

またコストや工数を極限まで効率化しなければならない状況では、できるだけ既存のIPやリファレンスを採用することが求められています。しかしながらこのようなIPやリファレンスデザインは、ますますブラックボックス化してしまい、最終的な実機デバッグにおいて、より高度な検証が必要になってきています。

問題は切り分けてしまえば単純な原因で発生していることがほとんどです。実機デバッグにおいても同時性のある多面的なデバッグをすることにより、スマートにコストと工数を削減する方法を考えてもよいのではないでしょうか?

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

図4 DDRアナライザによる初期化動作の確認

図4 DDRアナライザによる初期化動作の確認 図5 DDRアナライザによる同一アドレスの確認例

図5 DDRアナライザによる同一アドレスの確認例 図6 DDRアナライザとオシロスコープの連動

図6 DDRアナライザとオシロスコープの連動