それでもロジック・アナライザは使いたくない!?:いまさら聞けないロジック・アナライザ入門(4)(1/2 ページ)

オシロスコープはよく使うけどロジアナはできれば使いたくない、という技術者をターゲットに使いこなしのポイントを紹介

実機の環境はシミュレーションのように理想的ではない。実機で発生しているイベントをリアルタイムに観測できるツールはロジック・アナライザ(ロジアナ)だけだ。本稿では、これからロジアナを使ってみようと考えている読者を対象に、ロジアナの測定原理から、実機デバッグで役に立つテクニックまで順に解説していく。(編集部)

連載1から3回目まで、いろいろな切り口でロジック・アナライザについて語ってきました。しかしながら、やはりロジック・アナライザを引っ張り出してくるのは面倒だし、オシロスコープはよく使うけど、ロジアナはできれば使いたくないというエンジニアは少なくないと思います。今回はこのような読者をターゲットにそのあたりのポイントを少し掘り下げてみたいと思います。

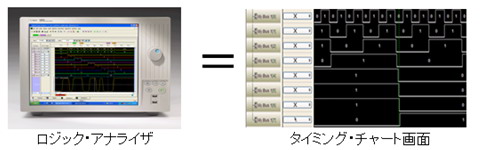

面白いことに昔から日本では、ロジアナ=タイミング・チャートのイメージが強く(図1)、海外ではロジアナ=リアルタイム・デバッグツールとして広く認知されています。

確かにロジック・アナライザの普及期には、多くのエンジニアがデバッグピンを立てて、タイミング・チャートでスキューやグリッチなどの問題現象を追いかけていました。しかし今ではFPGAやASICなどロジック回路がチップ内部に集積され外部に信号が出なくなりました。またこれらのチップには便利なシミュレータやデバッグツールもそろっており、よほどのことがない限りこのようなデバッグを行う必要はありません。このためオシロスコープでチップ間の伝送線路のシグナル・インテグリティをチェックする方がより重要になってきました。

また昔はCPU周りのバスをステートでサンプリングし、逆アセンブル表示とソースコードの相関を取りながらデバッグしていましたが、CPUに大容量のキャッシュが標準的に搭載されるようになるとJTAGデバッグが主流になりました。またソフトウェアの開発ツールもシステムの肥大化、複雑化の流れとともに発展し非常に便利になってきています。

以上のことからロジック・アナライザなんて過去の遺物だ、ロジック・アナライザを持ち出すようじゃ終わりだねと思っている方も多いと思います。しかしながら知らないうちにデバッグにはまっていたりしませんか? もしくはオシロスコープでロジック・イベントを追いかけて苦労していませんか?

意外と知られていないロジック・アナライザの進化

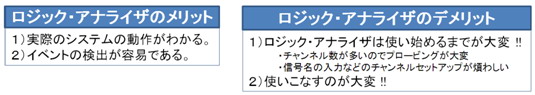

ロジック・アナライザは、近年ターゲット・システムの実際の動作を可視化しデバッグするツールとして進化してきています。まずはロジック・アナライザのメリット、デメリットを以下に簡単にまとめます。

ロジック・アナライザの最大のメリットは、実際のシステムの状況をリアルタイムにモニタできることです。また「あるアドレスにWriteしたとき」をイベントとして検出し、オシロスコープやICE、プロアナなどにトリガ連携することができます。

しかしシステムの挙動をリアルタイムにモニタしても、単に0/1のタイミングをチャートで見るだけでは、システム設計に関係するほかのエンジニアにはよく分かりません。しかしながらシステム上をやりとりしているメモリや画像などのデータをフォーマットに合わせてコマンドや画像にデコードすれば誰でも簡単に理解することができます。

しかもトリガイベントやプロービングの煩わしさの問題も、上位のコマンドや垂直同期イベント名でトリガリングすれば非常に簡単です。ロジック・アナライザは、いろいろ応用が利く製品なので、すべての機能を使いこなすのは少し大変かもしれません。しかしながら用途を決めて最適化すれば手軽に使用することができます。

またプローブについては前回で説明したとおり最近では手軽に使えるコネクタレスのプローブやアプリケーションに特化した専用プローブがありますので、プローブとアナライザをコネクタで接続してセットアップ・ファイルを開けばすぐに使用できるようになっています。

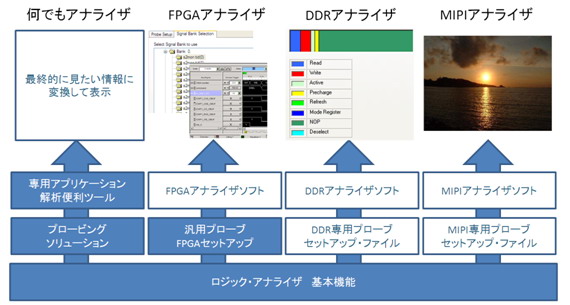

以上のことからロジック・アナライザは、アプリケーションに合わせてプローブとセットアップ、専用解析ソフトウェアアプリケーションを組み合わせれば「何でもアナライザ」になる可能性を秘めています(図2)。

それではFPGAアナライザやDDRアナライザを例に、どのようにロジック・アナライザがデメリットを克服して進化してきたのか確認していきましょう。

FPGAアナライザ

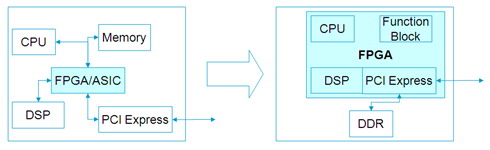

近年、FPGAは大規模、高集積、高速化が進み、CPUやI/Oコントローラなどの複雑な機能ブロックもIP化され、非常に複雑なハードウェアを手軽にFPGA内部で構成できるようになりました。

しかもFPGAは、シミュレータやデバッグツールなどFPGAベンダ純正の開発ツールが整備されており快適な開発環境が整っています。しかしながらFPGAベンダの標準ツールは、FPGA内部にロジック・アナライザ回路を組み込むため、FPGA内部のブロックRAMなどのリソースを消費せざるを得ない部分があります。

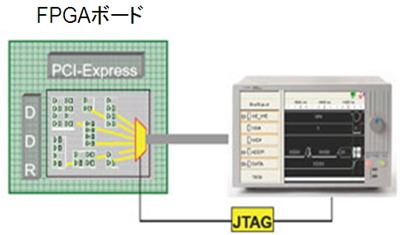

またDDRメモリや外部I/OはFPGAのクロックとは非同期になるため、実システムになるとシミュレーションのようにはいかないということも多々あります。そこでFPGA内部の信号を未使用ピンに引き出せば、ロジック・アナライザで内部の信号の状況をリアルタイムでモニタできますが、従来のロジック・アナライザの煩わしさが気になります。しかも違うポイントを観測したい場合には再度FPGAの配置配線をしなければなりません。

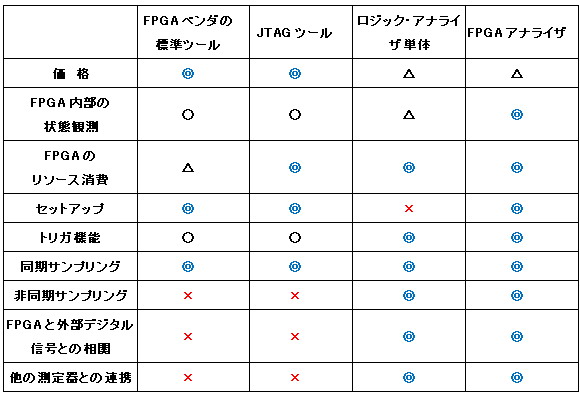

そこで登場してきたのがロジック・アナライザベースのFPGAアナライザです。ご参考までにFPGAの各種デバッグツールの比較データを以下に示します。

FPGAアナライザは、FPGA内部のデバッグコア(マルチプレクサ・コア)経由で観測したい内部の実信号をまるでシミュレータのように信号名を選択するだけでFPGA内部のノードの信号をJTAG経由で切り替えて、簡単にモニタすることができます。しかも観測したい信号やデバッグコアについてはFPGAベンダの環境からシームレスに構成することができます。

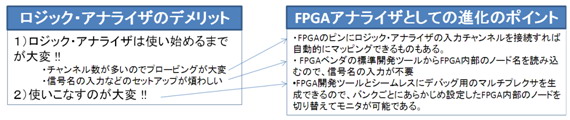

FPGAアナライザは、以下のとおりロジック・アナライザの従来のデメリットを克服して進化してきた製品だと考えることができます。

それからもう1つ、ロジック・アナライザは、いまだに高級高額測定器だと思っている方も多いのではないでしょうか? 実は、現在のロジック・アナライザの価格は、驚くほど安価になり、34チャンネル程度のFPGAアナライザの構成であれば、プローブ込みでも175万円程度で手に入ります。確かに同期2GHzの高性能ロジック・アナライザ・モジュールなどは400万円以上しますが、普及型のロジック・アナライザは、オシロスコープの広帯域化のような果てしない技術革新を要求されるよりも、デバッグの基本ツールとして使い勝手の向上を要求されてきたため、価格対性能比で見ると驚くほど低価格になってきています。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

図1 ロジック・アナライザ=タイミング・チャート?

図1 ロジック・アナライザ=タイミング・チャート? 表1 ロジック・アナライザのメリットとデメリット

表1 ロジック・アナライザのメリットとデメリット 図2 ロジック・アナライザから何でもアナライザへ

図2 ロジック・アナライザから何でもアナライザへ 図3 FPGAアナライザ

図3 FPGAアナライザ 図4 最近のSystem on FPGAの例

図4 最近のSystem on FPGAの例 表2 FPGAの各種デバッグツールの比較データ

表2 FPGAの各種デバッグツールの比較データ 図5 FPGAアナライザの概念図

図5 FPGAアナライザの概念図 表3 FPGAアナライザとしての進化ポイント

表3 FPGAアナライザとしての進化ポイント