東芝の2つの次世代ゲート駆動技術がSiCデバイスの損失削減に寄与、ISSCCで発表:組み込み開発ニュース(2/2 ページ)

スイッチドキャパシター回路のキャパシター数削減と駆動損失削減を両立

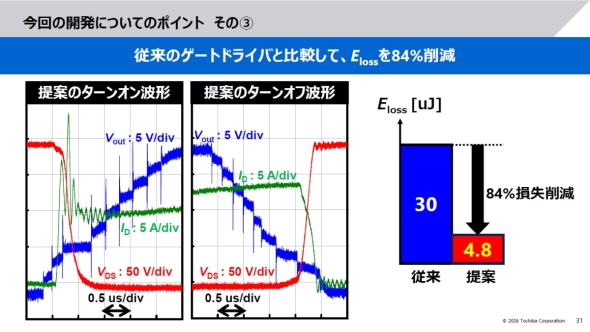

もう1つの研究成果である低損失ゲートドライバーでは、パワー半導体を駆動するゲートドライバICの損失を削減する「スイッチドキャパシター回路」で必要とされるキャパシターの数を削減しながら、同回路を適用しない場合と比較して84%の駆動損失の削減を実現した。

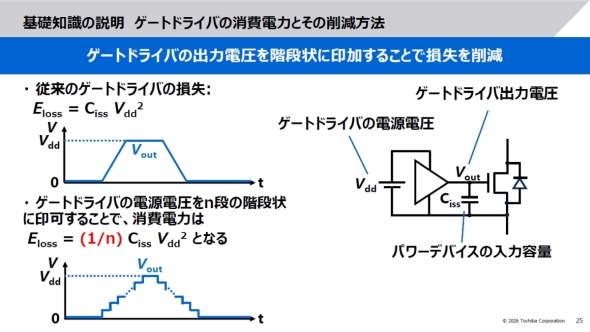

従来のゲートドライバICは、パワー半導体の動作周波数や電流が増えるとデバイスが大型化し、それに比例して駆動損失も増加していた。このことは、システムの電力効率向上や小型化を妨げる要因にもなっている。

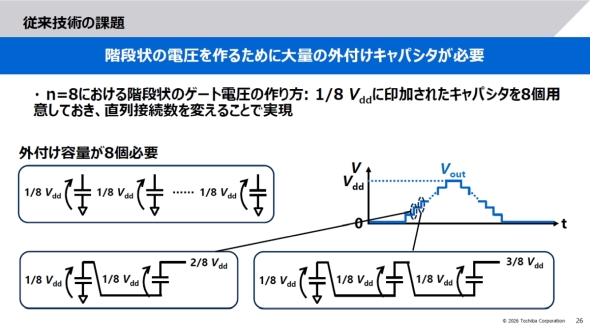

そこで駆動損失を削減する方法として採用されているのがスイッチドキャパシター回路だ。ゲートドライバICの電源電圧をn段の階段状に印可することで消費電力をn分の1に削減することができる。階段の段数を増やせば消費電力の削減効果は大きくなるものの、必要とされるキャパシターの数も増え、部品数が多くなり、小型化が難しくなってしまうという課題があった。

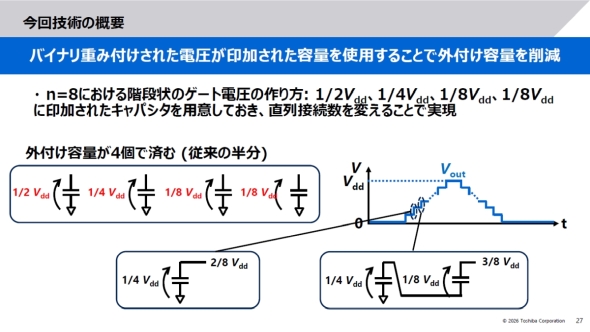

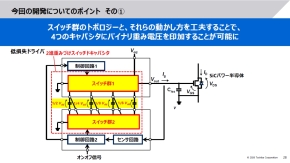

今回開発した低損失ゲートドライバーは、キャパシターの容量と印可電圧を2進数で重み付け(バイナリ重み付け)するとともに、独自のスイッチ接続構成を採用することで、必要になるキャパシターの数を削減することに成功した。従来の手法で、n=8の階段状のゲート電圧を作るには8個のキャパシターが用意しなければならない。

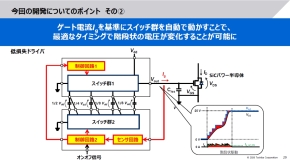

東芝が開発した新手法では、バイナリ重み付けされた電圧が印加されたキャパシターの容量を使用することで、4個のキャパシターでn=8の階段状のゲート電圧の生成が可能になった。また、ゲート電流Igを基準に、キャパシターを直列接続するスイッチ群を自動で動かすことにより、最適なタイミングで階段状の電圧を変化させられるという。

低損失ゲートドライバーの技術ポイント。スイッチ群のトポロジーと動かし方で4個のキャパシターにバイナリ重み電圧を印加できる(左)。ゲート電流Igを基準にスイッチ群を自動で動かすことで、最適なタイミングで階段状の電圧が変化させられる(右)[クリックで拡大] 出所:東芝

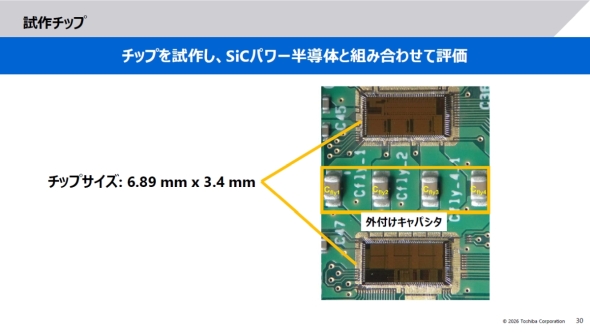

低損失ゲートドライバーの技術ポイント。スイッチ群のトポロジーと動かし方で4個のキャパシターにバイナリ重み電圧を印加できる(左)。ゲート電流Igを基準にスイッチ群を自動で動かすことで、最適なタイミングで階段状の電圧が変化させられる(右)[クリックで拡大] 出所:東芝この低損失ゲートドライバーに基づくゲートドライバICを試作し、4個のキャパシターと組み合わせて評価を行ったところ、従来のゲートドライバICと比べて駆動損失を84%削減できることを確認した。

なお、パワー半導体のゲートドライバICの駆動損失を低減する研究も幾つか発表されているが、ディスクリート素子を対象にした実証が多い。今回は、駆動対象がフルSiCモジュールであり、大容量のパワーモジュールでも駆動損失削減効果が得られることを実証した点に大きな意義があるという。

関連記事

自動車に不可欠なモーターとパワー半導体、東芝の戦略は

自動車に不可欠なモーターとパワー半導体、東芝の戦略は

車載用半導体にどのように取り組むのか。東芝デバイス&ストレージが説明会を開き、戦略を紹介した。 電力損失を半減したトレンチ型SiC-MOSFETチップ4品種を開発

電力損失を半減したトレンチ型SiC-MOSFETチップ4品種を開発

三菱電機は、EVや再生可能エネルギー用電源システム向けのトレンチ型SiC-MOSFETチップ4品種のサンプル提供を開始した。独自構造により、従来のプレーナー型と比べて電力損失を約50%低減し、低消費電力化に貢献する。 ロームとインフィニオンがSiCパッケージを共通化、調達の柔軟性を拡大へ

ロームとインフィニオンがSiCパッケージを共通化、調達の柔軟性を拡大へ

ロームとInfineon Technologies(インフィニオン)は、SiCパワーデバイスのパッケージを共通化する協業を開始した。両社から互換製品を調達できるようになり、設計や調達の利便性が高まる。 山形工場にSiCエピタキシャルウエハーの建屋が完成、2026年に稼働

山形工場にSiCエピタキシャルウエハーの建屋が完成、2026年に稼働

レゾナックは、レゾナック・ハードディスクの山形工場で、SiCエピタキシャルウエハーの生産建屋の竣工式を開催した。各種設備を導入して生産に向けた準備を進め、2026年に稼働する予定だ。 第4世代SiC MOSFETが中国向け新型BEVのトラクションインバーターに採用

第4世代SiC MOSFETが中国向け新型BEVのトラクションインバーターに採用

ロームの第4世代SiC MOSFETベアチップを搭載したパワーモジュールが、トヨタ自動車の中国市場向け新型クロスオーバーBEV「bZ5」のトラクションインバーターに採用された。 SiCデバイスの効率を最大化する絶縁型サーミスタ、すぐそばで動作温度を測れる

SiCデバイスの効率を最大化する絶縁型サーミスタ、すぐそばで動作温度を測れる

村田製作所は、「人とくるまのテクノロジー展 2025 YOKOHAMA」において、パワー半導体用NTCサーミスタ「FTIシリーズ」を展示した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

コーナーリンク