エッジでAIモデルのリアルタイム学習が可能に、TDKのスピンメモリスタ:CEATEC 2024

TDKは、「CEATEC 2024」において、人の脳を模倣したニューロモルフィックデバイスを構成するメモリスタを独自のスピントロニクス技術で実現した「スピンメモリスタ」を披露した。

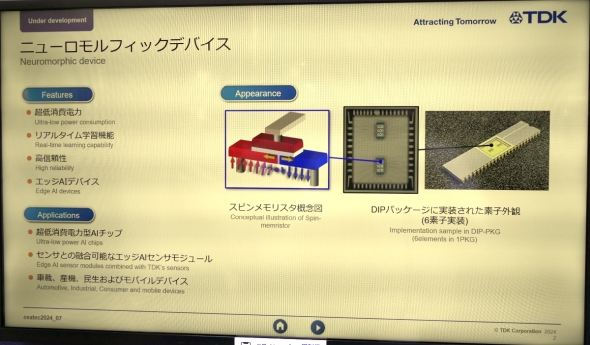

TDKは、「CEATEC 2024」(2024年10月15〜18日、幕張メッセ)において、人の脳を模倣したニューロモルフィックデバイスを構成するメモリスタを独自のスピントロニクス技術で実現した「スピンメモリスタ」を披露した。ニューロモルフィックデバイスは現行の半導体技術と比べてAI(人工知能)モデルを処理する際の消費電力を100分の1に削減できる可能性がある。今回展示したのは、6素子分のスピンメモリスタを実装したDIPパッケージだが、2027年をめどにより多くの素子をチップ上に集積することを目指す。実用化の目標は2030年だ。

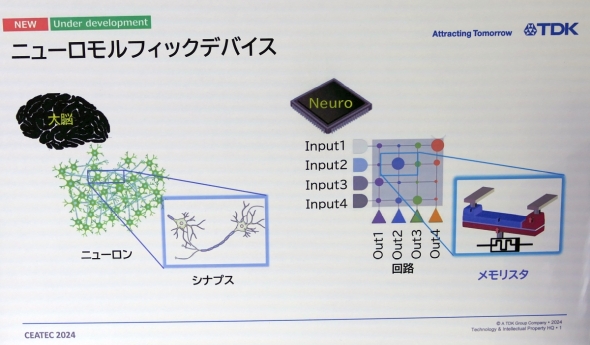

脳の電気的な振る舞いではニューロンをつなぐシナプスが重要な役割を果たす。そして、脳を模倣したニューロモルフィックデバイスのシナプスに当たるのが、電荷に応じて伝導度や抵抗値が変化する電気素子のメモリスタだ。

メモリスタの開発では、ReRAM(抵抗変化メモリ)やPCM(相変化メモリ)といった不揮発性メモリが用いられてきた。一方、スピンメモリスタは、TDKがHDDヘッドや磁気センサーの開発で積み重ねてきたスピントロニクス技術に基づいており、磁気抵抗効果を利用している。「従来の不揮発メモリと比べて応答性とデータ保持特性が優れており、メモリスタに最適だと考えている」(TDKの説明員)という。

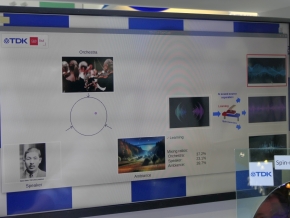

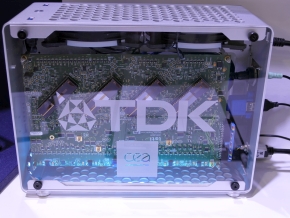

今回の展示では、6素子分のスピンメモリスタを集積するDIPパッケージを4つ組み合わせたシステムを用いた音声分離のデモンストレーションを披露した。オーケストラ演奏と講演を行う人の声、自然環境音を合成した音源を学習し、これら3つの音の内1つだけを分離するという内容だが、この合成比率を自在に変更しても、スピンメモリスタを用いたシステムでリアルタイムで学習することで正確に音声分離できることを示した。「スピンメモリスタは24素子しかないので、デモンストレーションにおけるAIモデル学習の全てはカバーできないが、一部を担うように設定している」(同説明員)。

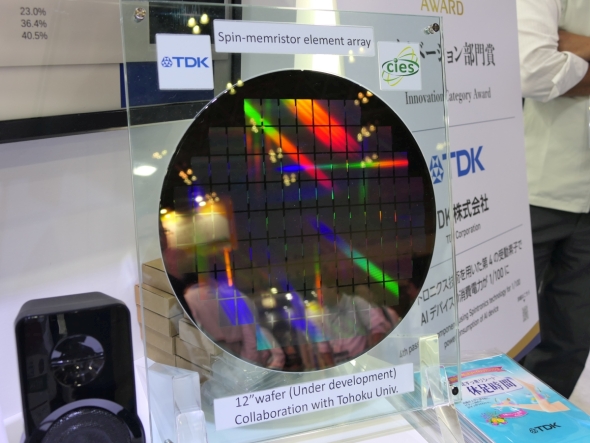

東北大学の協力により、スピンメモリスタの素子アレイを作り込んだ12インチウエハーも展示した。これは、一般的な半導体プロセスを用いて製造できることの証であり、今後の実用化に向けてはチップ上へのメモリスタの集積度を高めていくことが必要になる。なお、磁気抵抗効果を利用するスピンメモリスタの素子はMRAM(磁気抵抗メモリ)と互換性があるためファウンドリーなどでの量産が可能だ。

TDKのスピンメモリスタは「CEATEC AWARD 2024」のイノベーション部門を受賞している。

関連記事

脳型AI半導体のBrainChipが第2世代IPを投入、エッジ活用に向け本格提案

脳型AI半導体のBrainChipが第2世代IPを投入、エッジ活用に向け本格提案

脳の構造を模倣するニューロモーフィック技術を活用したAI半導体を手掛けるオーストラリアのBrainChipが、第2世代IPとして2023年9月のリリースを計画している「Akida 2.0」について説明した。 脳や神経機能を発現可能な4端子メモリスタの人工シナプス素子を開発

脳や神経機能を発現可能な4端子メモリスタの人工シナプス素子を開発

大阪大学は、4端子のメモリスタを用いた人工シナプス素子を開発し、生体が学習や行動する際に働く脳および神経系の情報伝達や処理に関わる連合性、変調性、相関性など高度な機能の実証に成功した。 人間の脳のように振る舞う汎用人工知能を開発するための方法論を標準化

人間の脳のように振る舞う汎用人工知能を開発するための方法論を標準化

東京大学は、汎用AIなどのソフトウェアを実装する際の仕様情報となる脳参照アーキテクチャデータ形式と、それを用いた開発方法論を標準化した。 脳の空間認知機能を再現する、小型の脳型AIハードウェアを開発

脳の空間認知機能を再現する、小型の脳型AIハードウェアを開発

東芝は、ジョンズホプキンス大学と共同で、小型の脳型AIハードウェアを開発し、海馬の空間認知機能の一部を模倣・再現することに成功した。脳機能研究の進展や、高い空間認知能力が求められる自律型ロボットなどの小型化、低電力化に貢献する。 AIに最適な脳型LSI、東北大が脳機能のモジュール化で2019年度に実現へ

AIに最適な脳型LSI、東北大が脳機能のモジュール化で2019年度に実現へ

東北大学の電気通信研究所は、2014〜2019年度のプロジェクトで、AI(人工知能)に最適な脳型LSIの開発を進めている。脳機能をモジュール化して計算効率を高め、人間の脳と同等レベルの処理能力と消費電力を持つ脳型LSIの実現につなげたい考えだ。 デンソーがクルマに載せられるAIの開発に注力、「かなり早めに出せる」

デンソーがクルマに載せられるAIの開発に注力、「かなり早めに出せる」

デンソーが東京都内で報道陣向けにAI(人工知能)取材会を開催。自動運転やADAS(高度運転支援システム)向けでAIを実用化するために開発しているさまざまな技術を、デモンストレーションで披露した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク