2nm半導体プロセスの開発は順調、ナノシートトランジスタの完成度は80%以上:材料技術(2/2 ページ)

CFETが今後の重要なプロセスアーキテクチャ

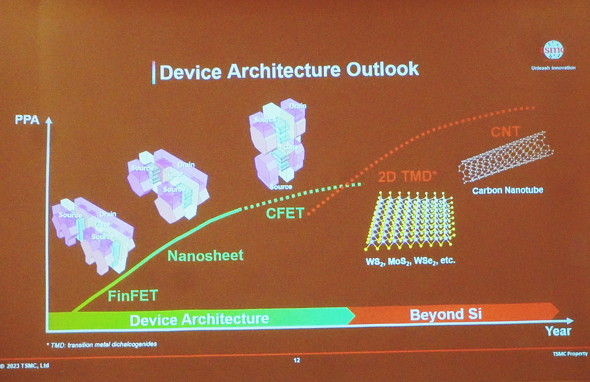

半導体を利用するトランジスタで採用されるアーキテクチャ(構造)の主流は近年、シリコンの基板上に選択拡散法によって不純物を添加する「プレーナー型」から立体構造の「FinFET」へと性能の向上を目的に変化している。しかし、現在は、さらなる性能の向上を目指し、FinFETのフィン(シリコン表面のソース/ドレイン領域)を真横に倒したようなチャネル構造「ナノシート構造」に主流は変わろうとしているという。

「ナノシート構造以外にも、TSMCでは、Pチャネル型MOSFETとNチャネル型MOSFETを垂直に積層したコンプリメンタリFET(CFET)を今後の重要なプロセスアーキテクチャだとみている。CFETは、配線とプロセスの複雑さを解決できれば、配線密度を1.5〜2倍に高められる見込みだ。また、強い層内共有結合と弱い層間ファンデルワールス力によって結合した層状化合物である2次元材料やカーボンナノチューブを活用し、加工の微細化や省電力を実現していく」(ジャン氏)

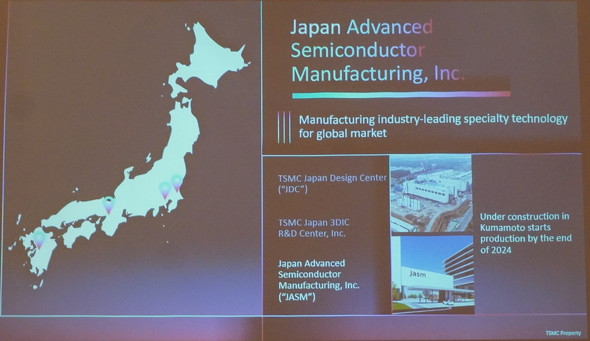

2024年の完成に向けて熊本県で半導体工場の建設プロジェクトを推進

日本国内での展開について、TSMCでは、先端半導体の研究を行う施設として、2020年に「TSMC Japan Design Center Yokohama(横浜市西区)」を、2022年に「TSMC Japan Design Center Osaka(大阪市中央区)」を設立した。2021年には、次世代半導体パッケージング技術の研究/開発を行う施設として「TSMCジャパン3DIC R&Dセンター」を開設している。

TSMC ジャパン 代表取締役社長 小野寺誠氏は「TSMCジャパン3DIC R&Dセンターは、台湾以外の研究開発拠点でクリーンルームを備えている唯一の拠点だ。研究/開発向けの装置も豊富に用意してあり、さまざまなパッケージング技術の開発を行っている」と説明した。

現在は、TSMC、ソニーセミコンダクタソリューションズ、デンソーが出資する「Japan Advanced Semiconductor Manufacturing(JASM)」が、2024年の完成に向けて、熊本県で半導体工場の建設プロジェクトを推進している。

日本での売上高に関して、国内でオフィスを設立した1997年は1億5000万ドルだったが、2010年には6億ドルを記録し、2022年には38憶ドルに達しており、堅調に売上を伸ばしている。日本へのウエハーの出荷枚数は、1997〜2022年の累計で921万2000枚を達成している他、2022年だけで130万枚を記録するなど増やし続けているという。

加えて、2022年に顧客から受注したカスタムチップのうち2464件の製品でテープアウト(IC化)を迎え、カスタムチップの試作サービスでも既に1851件がテープアウトしている。これら製品の試作サービスでテープアウトしたもののうち1251件は大学向けだった。なお、これまでに国内にある45の大学でカスタムチップなどが採用された実績があるという。加えて、グローバルでは、大学の学生や教職員など学術関係者に向け、FinFETなどの技術育成プログラム「University FinFET Program」を展開している。

関連記事

TSMCの国内半導体ファウンドリーが12/16nmプロセスに対応、投資規模は1兆円へ

TSMCの国内半導体ファウンドリーが12/16nmプロセスに対応、投資規模は1兆円へ

台湾TSMCとソニーセミコンダクタソリューションズ、デンソーの3社は、TSMCが国内に建設を予定している半導体ファウンドリーの運営企業であるJASMに、デンソーが約3.5億米ドル出資すると発表した。JASMのファウンドリーは、12/16nmのFinFETプロセスに対応し生産能力も増強するため、設備投資額を約86億米ドル(約9800億円)に増やす。 TSMCが産総研内に評価用ライン構築、経産省の次世代半導体技術支援で

TSMCが産総研内に評価用ライン構築、経産省の次世代半導体技術支援で

経済産業省は2021年5月31日、「ポスト5G情報通信システム基盤強化研究開発事業」の「先端半導体製造技術の開発(助成)」における実施者として、「高性能コンピューティング向け実装技術」に関するTSMCなど、5件の採択を決定した。 TSMCはなぜ台湾外初となる3DICのR&D拠点をつくばに設立したのか

TSMCはなぜ台湾外初となる3DICのR&D拠点をつくばに設立したのか

台湾の半導体受託製造大手であるTSMCは2022年6月24日、茨城県つくば市の産業技術総合研究所つくばセンター内に設置した「TSMCジャパン3DIC研究開発センター」の開所式を行った。同センターでは半導体微細化の限界が予想される中、後工程の3次元パッケージ技術の量産を可能とするための技術開発を日本の材料メーカーや装置メーカー、研究機関との共同研究で実施する。 TSMCと協業し、マルチダイ設計に対する包括的な熱解析ソリューションを開発

TSMCと協業し、マルチダイ設計に対する包括的な熱解析ソリューションを開発

Ansysは、TSMCと協業し、TSMC 3DFabricを用いたマルチダイ設計に対する包括的な熱解析ソリューションを開発した。綿密な熱解析により、オーバーヒートによるシステムの故障を防ぎ、使用期間中の信頼性を向上する。 TSMCが半導体ファウンドリーを熊本県に設立、ソニーの半導体子会社が出資

TSMCが半導体ファウンドリーを熊本県に設立、ソニーの半導体子会社が出資

世界的な半導体大手の台湾TSMCは2021年11月9日、半導体に対する世界的な需要の高まりへの対応を目的に、22/28nmプロセスを皮切りとした半導体の製造受託サービス子会社「Japan Advanced Semiconductor Manufacturing 株式会社(以下、JASM)」を熊本県に設立することを正式に発表した。また、ソニーグループの半導体関連子会社であるソニーセミコンダクタソリューションズがJASMに少数株主として参画する。 TSMCが日本への工場建設を発表、2022年着工で2024年に稼働予定

TSMCが日本への工場建設を発表、2022年着工で2024年に稼働予定

台湾のファウンドリ大手であるTSMCは2021年10月14日、2021年第3四半期決算発表の場で、日本に半導体工場を建設することを発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

素材/化学の記事ランキング

- 核融合による実用発電を目指す計画の公式パートナー制度、その狙いを考える

- 「日本にもうひとつ太陽をつくる」計画の第1弾公式パートナーが決定

- 気液間の物質移動、ガス吸収の考え方

- 100%植物原料由来のPEFフィルムを開発、高い剛性とガスバリア性を達成

- 【クイズ】国内の「錘」の減少率とは?

- 新入社員に読んで欲しい鉄鋼材料の基礎知識まとめ(Part1)

- 世界初のフッ素フリーネガ型ArF液浸レジスト、AI半導体向け先端ノードに対応

- 日本ゼオンが単層カーボンナノチューブ生産能力を数十倍へ、電池需要急増

- 100%廃棄ポリエステルから再生したモノマーを数十トン規模で製造

- 千葉で油化ケミカルリサイクル設備の商業運転開始、使用済みプラを再資源化

コーナーリンク

TSMC ジャパン 代表取締役社長 小野寺誠氏[クリックで拡大] 出所:TSMC

TSMC ジャパン 代表取締役社長 小野寺誠氏[クリックで拡大] 出所:TSMC