TSMCはなぜ台湾外初となる3DICのR&D拠点をつくばに設立したのか:FAニュース(1/2 ページ)

台湾の半導体受託製造大手であるTSMCは2022年6月24日、茨城県つくば市の産業技術総合研究所つくばセンター内に設置した「TSMCジャパン3DIC研究開発センター」の開所式を行った。同センターでは半導体微細化の限界が予想される中、後工程の3次元パッケージ技術の量産を可能とするための技術開発を日本の材料メーカーや装置メーカー、研究機関との共同研究で実施する。

台湾の半導体受託製造大手であるTSMCは2022年6月24日、茨城県つくば市の産業技術総合研究所つくばセンター内に設置した「TSMCジャパン3DIC研究開発センター」の開所式を行った。同センターでは半導体微細化の限界が予想される中、後工程の3次元パッケージ技術の量産を可能とするための技術開発を日本の材料メーカーや装置メーカー、研究機関との共同研究で実施する。

「TSMCジャパン3DIC研究開発センター」は2021年3月の設立だが、クリーンルーム施設が無事に完成したことであらためて開所式を行った。開所にあたりTSMC CEOのC.C.Wei(シーシー ウェイ、魏哲家)氏は「デジタル化が広がりを見せる中、エレクトロニクス製品の重要性はますます高まっている。半導体の微細加工技術の物理的な限界が近づく中で、3次元パッケージング技術が重要になってきている。グローバル半導体サプライチェーンにおいて、台湾は製造拠点として強みを持ち、日本は素材や装置で強みを持つ。これらの強みを組み合わせることで、半導体バリューチェーンの中で設計や開発、素材、装置全てが関係する形で新しい将来像を作りたい」と語っている。

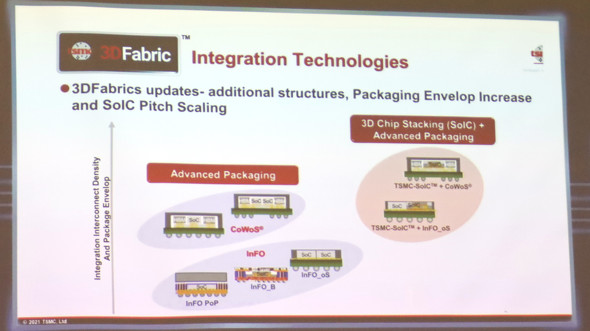

TSMCでは、次世代の半導体製造技術として、後工程で複数のチップを3次元で高密度に積層し1つの半導体のように機能させる3次元積層パッケージング技術に注力している。既に「3D Fabric」として、さまざな技術開発を進めており、台湾では量産工場なども計画している。

半導体プロセスは1つのチップ内により細かい回路を組み込む微細化を進めることで集積密度を高め進化を遂げてきた。製造技術や回路技術などの開発により、この集積密度の高まりは一定の比率で伸長を続けてきていたが、その物理的限界に徐々に近づいているとされている。現在でも最先端プロセスの製造ラインを構築するには莫大な投資が必要となっており、これから微細化をさらに進めていく中でさらに大きな投資が求められるようになってくれば、企業投資の面でもどこかで壁に突き当たるのが見えている状況だ。

そこで、前工程の微細化以外でも半導体の性能を高められる技術が求められており、その技術としてTSMCでは3次元パッケージング技術の研究開発に力を入れている。

TSMCジャパン3DIC研究開発センター センター長の江本裕氏は「微細化については当然変わらずに進めていき、3nmや2nmプロセスの開発も行っている。ただ、将来的に『ムーアの法則(半導体の回路集積密度が1年半〜2年で2倍になるとされる法則)』がスローダウンし、チップが安く作れなくなる。それでも成長を止めないための準備として3Dパッケージング技術の確立が必要になる」と述べている。

TSMCジャパン3DIC研究開発センターではこの3次元パッケージング技術の開発に向け、主に材料および製造装置における技術開発を進める役割を担う。人数は明らかにしなかったが、台湾で3DICの研究開発を行うメンバーと日本で新たに雇用したメンバーが半分ずついる状況で、さらにこれらにパートナー企業などが参画し、共同研究を行う。

パートナー企業や団体としては、材料メーカーでは、旭化成、イビデン、JSR、昭和電工マテリアルズ、信越化学工業、新光電気工業、住友化学、積水化学工業、東京応化工業、長瀬産業、日東電工、日本電気硝子、富士フイルム、三井化学が参加。また、装置メーカーとしては、キーエンス、芝浦メカトロニクス、島津製作所、昭和電工、ディスコ、東レエンジニアリング、日東電工、日立ハイテク、大学・研究機関からは産業技術総合研究所、先端システム技術研究組合(RaaS)、東京大学などの名前が挙がっているが「この中の企業だけに限定する形ではなく必要があればさらにオープンに進めていく」(江本氏)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク

TSMC CEOのシーシー ウェイ氏

TSMC CEOのシーシー ウェイ氏