スイッチング損失を20%削減した第3世代SiC MOSFETを開発:組み込み開発ニュース

東芝デバイス&ストレージは、従来製品と比べてスイッチング損失を約20%低減した、低オン抵抗の新しい「SiC MOSFET」を開発した。産業機器の省エネルギー化やカーボンニュートラルの達成に貢献する。

東芝デバイス&ストレージは2022年7月22日、従来製品と比べてスイッチング損失を約20%低減した、低オン抵抗の新しい「SiC(炭化ケイ素) MOSFET」を開発した。産業機器の省エネルギー化やカーボンニュートラルの達成に貢献する。第3世代のSiC MOSFETとして、同年8月下旬から量産する予定だ。

SiC MOSFETは、Si(シリコン) MOSFETと比べて、高耐圧、低損失化が可能だが、信頼性に課題があった。同社は既に、PNダイオードとSBD(ショットキーバリアダイオード)を並列に配置した、信頼性の高い第2世代のSiC MOSFETを開発している。

しかし、第2世代MOSFETは、SBDを内蔵したためにMOSFETとしての動作領域が減り、RonA(単位面積当たりのオン抵抗)や性能指数Ron×Qgdの増加に伴う損失が増えた。その結果、所望のオン抵抗を得ようとすると、大きなチップ面積が必要になり、コストが上がるという問題が出てきた。

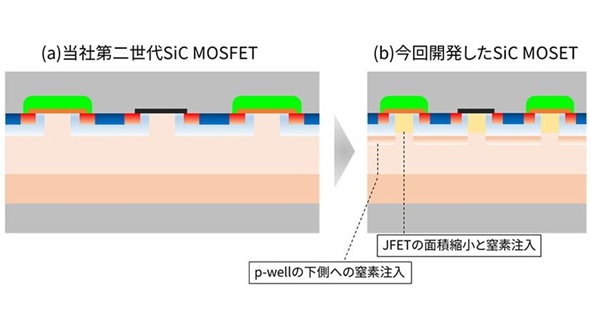

そこで、p型拡散領域の下側とJFET(接合型電界効果トランジスタ)領域に窒素を注入することで、内蔵SBDの電流を増やしつつ、JFETの面積と帰還容量を抑えたデバイス構造を開発。試作デバイスは、第2世代品と比べて、RonAを43%、性能指数を80%、スイッチング損失を約20%、それぞれ削減できた。また、SBDがRonAの変動を抑え、安定して動作することも確認した。

関連記事

独立分社する東芝デバイスカンパニーの成長をけん引するパワー半導体技術の実力

独立分社する東芝デバイスカンパニーの成長をけん引するパワー半導体技術の実力

東芝デバイス&ストレージがパワー半導体技術について説明。東芝から独立分社するデバイスカンパニーの成長をけん引することが期待されているパワー半導体事業だが、低耐圧と高耐圧のMOSFETで業界トップの性能を実現しており、次世代パワー半導体として期待されているSiCデバイスやGaNデバイスの開発にも注力している。 東芝がトリプルゲートIGBTを開発、3つのゲート電極でスイッチング損失を4割削減

東芝がトリプルゲートIGBTを開発、3つのゲート電極でスイッチング損失を4割削減

東芝は、インバーターやDC-DCコンバーターなどの電力変換器に広く用いられているパワー半導体のIGBTについて、電力のオンとオフが切り替わるスイッチング時の損失を従来比で最大40.5%低減できる「トリプルゲートIGBT」を開発したと発表した。今後、信頼性の確認など実用化に向けた開発を進めて、2023〜2024年に製品化を判断したい考え。 躍進する東芝パワー半導体、生産能力向上のカギは増床とIoT活用

躍進する東芝パワー半導体、生産能力向上のカギは増床とIoT活用

東芝デバイス&ストレージのディスクリート半導体の販売が好調だ。生産能力の増強を進めており、2021年度には売上高2000億円、営業利益率10%の実現を目指している。増床や生産性改善などを進めるディスクリート半導体の拠点「加賀東芝エレクトロニクス」(石川県能美市)の取り組みを紹介する。 自動車と民生に注力する三菱電機のパワーデバイス事業、12インチ化も着々

自動車と民生に注力する三菱電機のパワーデバイス事業、12インチ化も着々

三菱電機が2021〜2025年度の中期経営計画で重点成長事業の一つに位置付けたパワーデバイス事業の戦略を説明。産業、再エネ、電鉄などの分野をベースロードとしながら、今後は自動車と民生の分野に注力し、2020年度の売上高1480億円、営業利益率0.5%から、2025年度に売上高2400億円以上、営業利益率10%以上に引き上げる方針だ。 シリコンカーバイド(SiC)が電気自動車の普及に拍車

シリコンカーバイド(SiC)が電気自動車の普及に拍車

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回のテーマは電気自動車への搭載が進むSiCデバイスだ。 インフィニオンが電動車向けSiCパワーデバイスを強化、武器はIGBTからの移行しやすさ

インフィニオンが電動車向けSiCパワーデバイスを強化、武器はIGBTからの移行しやすさ

インフィニオンは、EV(電気自動車)向けのSiCパワーデバイスの展開を本格化させる。これまでハイブリッド車(HEV)など電動車向けに100万個以上の出荷実績があるIGBT搭載のモジュール「Hybrid PACK Drive」にSiC搭載版を用意し、自動車メーカーがこれまでと同じフットプリントのままインバーターをアップグレードできるようにする。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク