旧Xilinxが主導するAMDの組み込み向けロードマップ、CPUとFPGAのチップ内統合も:組み込みイベントレポート(3/3 ページ)

AMDとXilinxのAI開発プラットフォームを統合へ

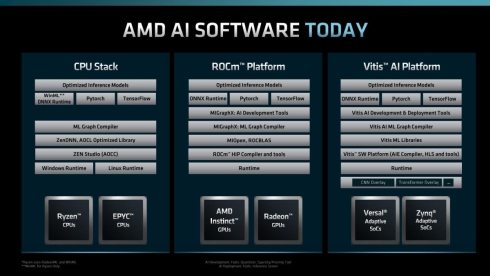

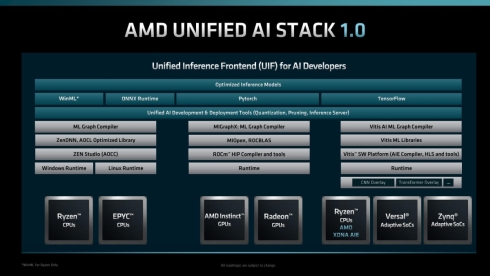

興味深いのはここからだ。現状のAMDのAI開発プラットフォームは、GPUの「Radeon Instinct/Radeon」に向けて提供される「ROCm」と、Versal/Zynq向けに提供される「Vitis」ということになるのだが(図11)、まず第1弾として全てのプラットフォームで共通に動作する“ガワ”として「Unified AI Stack 1.0」を提供する(図12)。

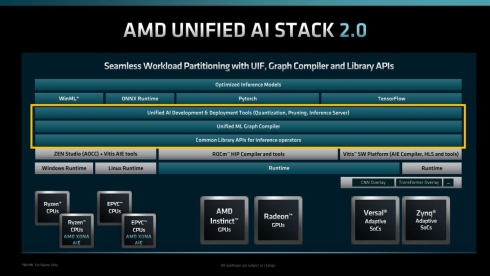

ところがその次の段階では、かなりの部分を共通化するとした(図13)。この「Unified AI Stack 2.0」が提供されるのは、CPUに「XDNA」としてAI Engine(-ML)が搭載されるZen 5世代が投入される2024年ごろと目される。

つまり、Unified AI Stack 1.0が2023年にまず投入され、これを最適化したものが2024年に投入される格好だ。この2.0世代で、CPUのAI Engineの最適化は「Zen Studio」に加えて「Vitis AIE tool」が利用されるというあたり、XilinxのACAP向け技術がそのままCPUに統合されていく、という格好になるわけだ。

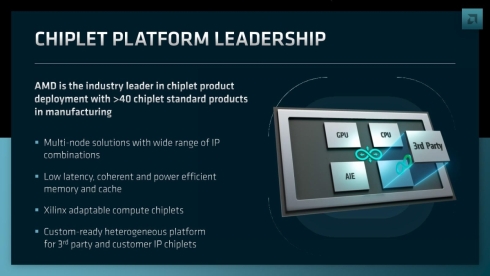

こうした流れの中では、例えば長期的にはCPUとFPGA/ACAPが同じパッケージの上でチップレットの形で統合されることもあり得るだろう(図14)。まだ統合は始まったばかりだから、今後どんな方向に向かってゆくか正確に示すのは難しいが、意外にシームレスにAMDとXilinxは製品ラインアップを融合させていきそうであり、AECGがそうした融合の作業を当面は担うことになるもようだ。

関連記事

AMDの組み込み部門となったザイリンクス、工場の無線化で5GとTSNをつなぐ

AMDの組み込み部門となったザイリンクス、工場の無線化で5GとTSNをつなぐ

ザイリンクスが産業機器向けを中心とした同社の事業展開について説明。2021年4月に発表したAIカメラ向けSOM製品「Kria」が高い評価を得ており、新パッケージの採用で大幅な小型化を果たした「UltraScale+」製品群の展開も好調だ。ローカル5Gなどの活用で進みつつある工場の無線化に向けて、5GとTSNをつなぐIPの開発も進めているという。 AMDがROS対応のロボット開発キットでNVIDIAに対抗、開発期間を約5分の1に短縮

AMDがROS対応のロボット開発キットでNVIDIAに対抗、開発期間を約5分の1に短縮

AMDは、SOM製品「Kria」の新たなラインアップとして、オープンソースのロボット開発フレームワーク「ROS 2」をネイティブでサポートする「Kria KR260ロボティクス・スターターキット」を発表。NVIDIAの競合ソリューションと比較して、ソフトウェア開発期間が約5分の1、消費電力1W当たりの性能が8倍以上、レイテンシが3分の1以下になるという。 ザイリンクスは5G通信分野の売り上げ好調、ペン氏CEO就任以来の事業振り返り

ザイリンクスは5G通信分野の売り上げ好調、ペン氏CEO就任以来の事業振り返り

ザイリンクスは2021年5月14日、同社 社長 兼 CEOのビクター ペン(Victor Peng)氏が、2018年に就任して以来の事業成長に関する説明会を開催した。5Gネットワークや通信局向け事業の他、自動車や産業/科学/医療などの分野向け製品が大きく成長した。 ザイリンクスが事業方針を説明、AMDの買収でも“アダプティブ”を堅持

ザイリンクスが事業方針を説明、AMDの買収でも“アダプティブ”を堅持

ザイリンクスがオンラインで会見を開き事業方針を説明。2021年末にはAMDにいる買収が完了する予定だが、従来と変わらず適応型(アダプティブ)演算プラットフォームを推進する事業方針を堅持していくという。 組み込み機器向け「Ryzen」の演算性能は最大3.6TFLOPS、AIも動かせる

組み込み機器向け「Ryzen」の演算性能は最大3.6TFLOPS、AIも動かせる

日本AMDは、「第21回 組込みシステム開発技術展(ESEC2018)」において、組み込み機器向けのプロセッサ製品「AMD Ryzen Embedded V1000ファミリー」を展示した。 アルテラとザイリンクスがいないFPGA業界の行く末

アルテラとザイリンクスがいないFPGA業界の行く末

とがった企業が買収されて、その名前が消えていくのは寂しいですね……。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- IoTとは何かを問いただすため、まずは薪ストーブに熱電対センサーを取り付ける

- PCマウス原理でエレベーターの“ロープ”不要に AI保守を見据える日立HMAX戦略

- イチから全部作ってみよう(32)PythonでSQLを実行してデータベースを操作する

- ソフトウェアテスト自動化SDKをオープンソースで公開

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- 消費電力を10分の1に低減したグローバルシャッター搭載CMOSイメージセンサー

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- 電力を最大64%低減、エッジデバイスにも応用可能なモバイル向けプロセッサ

- 1.42×1.00×0.43mmの超小型反射形フォトインタラプタを開発

- 高温時のオン抵抗を3割削減、ロームの「第5世代SiC MOSFET」

コーナーリンク