日立がシリコン量子ビットの開発に向け前進、超伝導量子ビットを超えるか:量子コンピュータ(3/3 ページ)

トップダウン型のシリコン量子ビットで超伝導量子ビットを超える

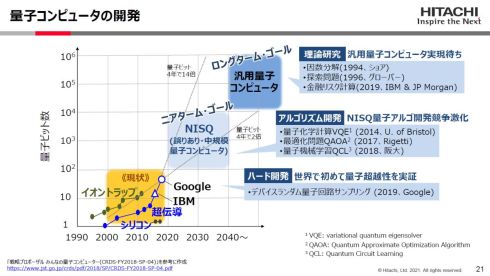

現在、ゲート型量子コンピュータの性能競争で最も進んでいるのが超伝導材料を用いた回路で量子ビットを実現している「超伝導量子ビット」だ。商用機となる「IBM Q System One」を2019年1月に発表したIBMや、2019年9月に世界で初めて量子超越性を実証したと発表したGoogleのゲート型量子コンピュータは、この超伝導量子ビットを用いている。

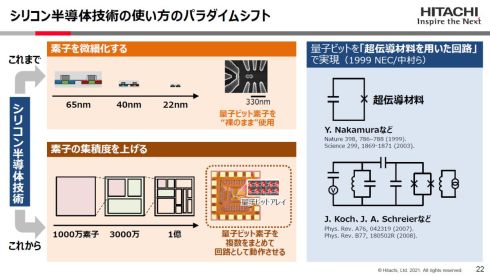

これに対して日立が取り組んでいるのが、古典コンピュータの技術進化に大きく貢献したシリコン半導体技術をベースに量子ビットを実現するシリコン量子ビットである。これまでのシリコン量子ビットの開発は、微細化した量子ビット素子を“裸のまま”使用するという方向性だったが、量子ビット素子の動作や制御が難しいという課題があった。水野氏は「回路として構成されている超伝導量子ビットは、1つ1つが大きいものの制御が容易だ。この特徴をシリコン量子ビットに応用し、素子の集積度を上げて量子ビット素子複数をまとめて回路として動作させるというコンセプトで開発を進めた」と語る。

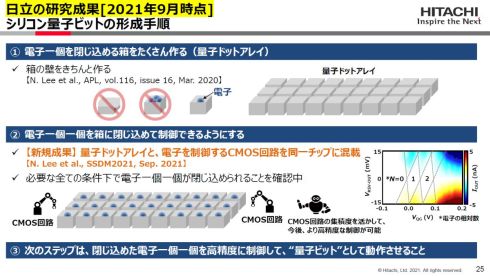

その開発成果の一つとなるのが「量子ドットアレイ」である。2021年9月開催の国際学会「SSDM2021(International Conference on Solid State and Materials)」では、電子1個だけを閉じ込めることができる箱をたくさん作る量子ドットアレイを形成し、これらの箱に電子1個1個を閉じ込めて制御するためのCMOS回路を同一チップに混載できる半導体プロセス「Q-CMOS」を発表している。

量子ドットアレイの数は、128量子ビットに相当する128個だ。「現在は、必要な全ての条件下で、箱それぞれに電子1個1個が閉じ込められていることを確認している段階。この確認を完了できれば、箱に閉じ込めた電子1個1個を高精度に制御して量子ビットとして動作させるステップに進む」(水野氏)という。

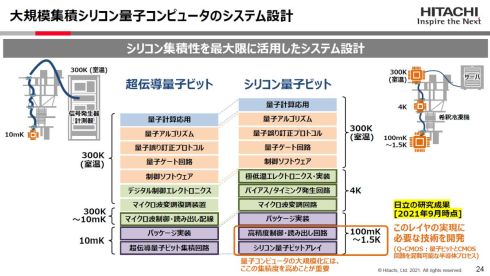

現在、開発で先行する超伝導量子ビットは、ヘリウムなどを用いた希釈冷凍機によって実現できる10mKという極低温環境に超伝導量子ビットの集積回路を配置する必要がある。この超伝導量子ビットの集積回路と、極低温環境の外側にある信号発生器や計測器をつなげて量子ビットの状態を観測することで量子コンピューティングを実現している。将来的に、量子ビットをより大規模にしていく場合には、現在外側に出している信号発生器や計測器の機能をシリコン半導体として集積し、極低温環境の内部に組み込む必要も出てくる。

日立が現在開発中のシリコン量子ビットは、量子ドットアレイと周辺の高精度制御・読み出し回路を混載することで、超伝導量子ビットで将来的に想定される極低温環境への機能取り込みを先行して実現するものになっている。また、シリコン量子ビットが超伝導量子ビットと大きく異なる特徴の一つとして、100m〜1.5Kという10mKよりもはるかに実現が容易なレベルの極低温環境で済むことが挙げられる。水野氏は「ホット量子シリコンビットとも言われており、希釈冷凍機の構成を簡素にできるし、量子ビットのさらなる大規模化にもつなげられる」と強調する。

超伝導量子ビットとシリコン量子ビットにおけるシステム設計の違い。超伝導量子ビットは、超伝導量子ビットの集積回路を10mKという極低温環境に置く必要があるが、シリコン量子ビットは100m〜1.5Kで済む(クリックで拡大) 出典:日立製作所

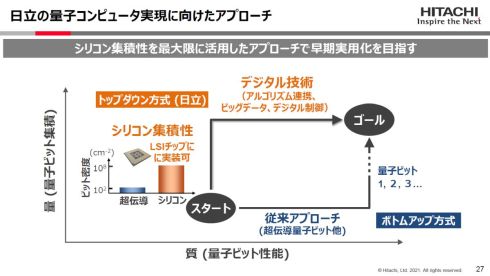

超伝導量子ビットとシリコン量子ビットにおけるシステム設計の違い。超伝導量子ビットは、超伝導量子ビットの集積回路を10mKという極低温環境に置く必要があるが、シリコン量子ビットは100m〜1.5Kで済む(クリックで拡大) 出典:日立製作所汎用量子コンピュータの実現に向けた超伝導量子ビットなどを用いる従来のアプローチを「ボトムアップ型」とすると、日立が取り組むシリコン量子ビットによるアプローチは「トップダウン型」になる。シリコンの集積性により量子ビットの大規模化が容易であり、古典コンピュータで開発が進むさまざまなデジタル技術も活用できるからだ。

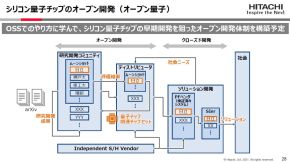

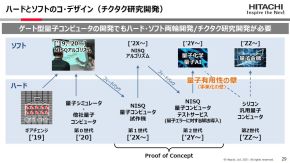

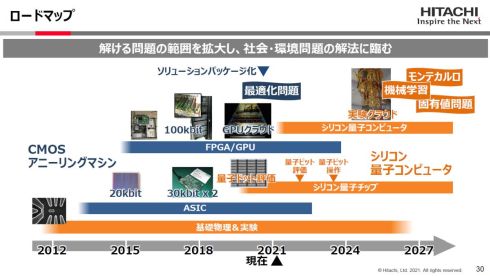

水野氏は「シリコン量子ビットを用いた量子コンピュータの開発では、オープンソースソフトウェアのやり方に学んで“オープン量子”といえるようなオープンな体制で早期開発を目指す。また、量子有用性の壁を超えるためには、CMOSアニーリングと同様にソフトウェアやアプリケーションと連携したチクタク開発も重要になってくるだろう。2027年から始まる中計期間中には、シリコン量子ビットを用いた量子コンピュータの実験的なクラウドを公開したい」と述べている。

関連記事

量子アニーリング提唱者の西森氏が語る量子コンピューティングの現在

量子アニーリング提唱者の西森氏が語る量子コンピューティングの現在

2020年11月16〜27日にオンラインで開催された「第30回 日本国際工作機械見本市(JIMTOF 2020 Online)」において、主催者セミナーとして東京工業大学 科学技術創成研究院 特任教授の西森秀稔氏が登壇。「量子コンピュータ研究開発の現状と展望」をテーマに講演を行った。本稿ではその内容を紹介する。 数年後に古典コンピュータを超える量子コンピュータ、IBMは事業化に舵を切る

数年後に古典コンピュータを超える量子コンピュータ、IBMは事業化に舵を切る

日本IBMが量子コンピュータに関する取り組みの最新状況について説明。IBMが1970年代から研究を続けてきた量子コンピュータの現在の開発状況や、日本での事業展開、今後の実用化に向けた取り組みなどについて紹介するとともに、「量子コンピュータの事業化が既に始まっている」ことなどを訴えた。 国内24社が量子産業創出に向けQ-STARを設立、活動のベースとなる「QRAMI」とは

国内24社が量子産業創出に向けQ-STARを設立、活動のベースとなる「QRAMI」とは

量子技術による新産業創出協議会(Q-STAR)が2021年9月1日、設立会員24社による総会の承認を得て正式に発足した。Q-STARは今後、4つの部会を中心に産業界が主体となって「量子産業の創出」を目指す方針である。 その名も「kawasaki」、国内初のゲート型商用量子コンピュータが稼働

その名も「kawasaki」、国内初のゲート型商用量子コンピュータが稼働

東京大学とIBMは、日本初導入となるゲート型商用量子コンピュータ「IBM Quantum System One」が稼働を開始したと発表。設置場所は「新川崎・創造のもり かわさき新産業創造センター」で、東京大学が設立した量子イノベーションイニシアティブ協議会に参加する慶應義塾大学や、日本IBMを含めた企業11社を中心に活用を進めることになる。 東大が量子技術の社会実装に向け協議会設立、トヨタや日立など製造業も参画

東大が量子技術の社会実装に向け協議会設立、トヨタや日立など製造業も参画

東京大学は、量子コンピューティングをはじめとする量子技術の社会実装を目指す「量子イノベーションイニシアティブ協議会(QII協議会)」を設立した。同協議会には、産業界から、JSR、DIC、東芝、トヨタ自動車、日本IBM、日立製作所、みずほフィナンシャルグループ、三菱ケミカル、三菱UFJフィナンシャル・グループの9社が参加する。 「NISQ」による量子コンピュータ応用、「Amazon Braket」がハードルを下げる

「NISQ」による量子コンピュータ応用、「Amazon Braket」がハードルを下げる

AWSジャパンが量子コンピューティングサービス「Amazon Braket」や、量子コンピュータの技術動向について説明した。Amazon Braketは「全ての開発者、科学者の手に量子コンピューティングを」というコンセプトのフルマネージドサービスで、AWSの他のサービスと同様の手軽さで利用できるという。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

- 国産の高解像度宇宙X線望遠鏡の開発に成功

- 大容量X線画像データを8600分の1に即時圧縮するFPGAデータ処理基板を共同開発

- 声やスマホでの操作も不要、次世代スマートホームは「ビルトイン型」へ

- ドライブレコーダーの録画時間を最大10倍に延長する動画ソリューション

- 長期供給SoCを活用したMCU向け組み込みGUI開発ソリューションの提供を開始

- 産総研のフィジカルAIプロジェクトに迫る 10万年ギャップを超えろ!

コーナーリンク