謎の多い「Armv9」について今分かっていることをまとめる:Arm最新動向報告(14)(3/3 ページ)

「SVE2」は「SVE」+「NEON」だが若干の書き換えが必要

SVE(Scalable Vector Extension)2に関しては筆者の調査不足だったのだが、実は2019年3月に行われた「Linaro Connect Bangkok 2019」の中で、ArmはSVE2の概略を公開していた。そこで、その時の資料をベースにSVE2についてご紹介したい。

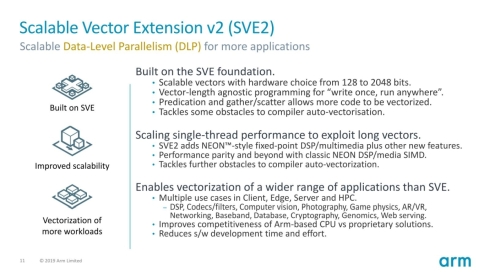

まずSVE2の基本的なコンセプトだが、SVEをベースにしながら(つまり、レジスタ構成や、128ビットから2048ビットまで128ビット単位でレジスタ長を拡張可能な特徴などはSVEそのまま)、SIMD演算のために開発された「NEON」風の命令セットを追加した、というのがSVE2の基本的なコンセプトである(図6)。

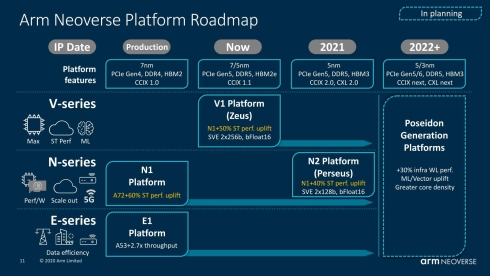

そもそもSVE自体はHPC向けに、それこそ算術演算をメインに実装した構成だったが、Arm自身「Neoverse V1/N2」ではNEONの代わりにSVEを実装することを明らかにしており(図7)、ところがそうなるとNEONで提供されていたもろもろの命令セットがないことが不足に感じられていたのだろう。

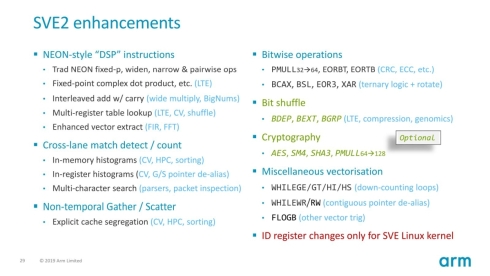

SVE2で具体的に拡張されたのがこちら(図8)。青字がNEONから移植された命令、緑字が今回新規追加された命令である。()内に書いてある内容は、その命令を利用する想定のアプリケーション例となる。ただし、SVE→SVE2は基本的に互換ではあるが、ID registerあたりは変更になるようで、ここだけ書き換えが必要になる。

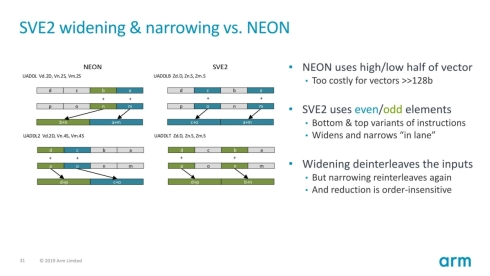

またNEONからSVE2でも若干の書き換えが発生する。NEONの場合SIMDレジスタのサイズが128ビットの固定長だったから、図9左側のようなデータ構成でも問題がなかった。ところがSVE2の場合、最大2048ビットまでレジスタ長が増えることになる。これを左詰めや右詰めで処理しようとした場合、「プログラムがレジスタ長を意識しなければならない」という、SVEの理念(レジスタ長に無関係にプログラムが記述できる)に反することになる。そこでSVE2では図9の右側のように、データの扱い方を変えることになったとしている。逆に言えば差は(今見えている限り)ここだけである。

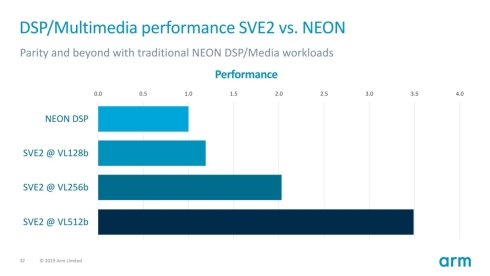

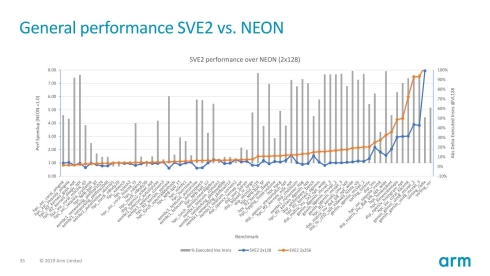

ちなみにArmの説明によれば、NEONのDSP命令をSVE2に切り替えることで、1.2倍(128ビット)〜3.5倍(512ビット)に性能改善できるという(図10)。また、絶対性能で言ってもNEONに比べて最大で8倍近い性能改善が得られるとしている(図11)。

図11 縦棒は右軸で、実行時間におけるSIMD命令の割合、折れ線は左軸でNEONを1.0とした場合の性能改善率となる。SIMD命令がマイナスというのは、利用していたNEON命令に相当するSVE2命令がなかった、という意味だろうか?(クリックで拡大)

図11 縦棒は右軸で、実行時間におけるSIMD命令の割合、折れ線は左軸でNEONを1.0とした場合の性能改善率となる。SIMD命令がマイナスというのは、利用していたNEON命令に相当するSVE2命令がなかった、という意味だろうか?(クリックで拡大)こちらもまだ命令セットの詳細などが明らかになっていない(SVE2のドキュメントはVLAのプログラミングガイドとサンプルコードを併せて近日発表という話だった)あたりは、Armv9のリリースタイミングがずれたことと無縁ではなさそうな気はするが、正式発表があった以上こちらも近日には詳細が出てくることを期待したい(現時点では、Armv9-Aの2021年3月版がこちらのWebサイトで公開されているだけである)。

関連記事

- ≫連載「Arm最新動向報告」バックナンバー

「Armv9」は「富岳」の技術で性能向上、「レルム」コンセプトでよりセキュアに

「Armv9」は「富岳」の技術で性能向上、「レルム」コンセプトでよりセキュアに

Armが最新アーキテクチャとなる「Armv9」を発表。日本のスーパーコンピュータ「富岳」向けに追加した拡張機能「SVE」をベースに開発した「SVE2」により機械学習やデジタル信号処理(DSP)の性能を大幅に向上するとともに、よりセキュアなコンピューティングを実現する「Arm Confidential Compute Architecture(CCA)」を導入するなどしている。 IntelとAMDを超えたArmのサーバ向けプロセッサ、実はソフトバンクのおかげ?

IntelとAMDを超えたArmのサーバ向けプロセッサ、実はソフトバンクのおかげ?

Armが開催した年次イベント「Arm DevSummit 2020」の発表内容をピックアップする形で同社の最新動向について報告する本連載。今回は、「Neoverseシリーズ」をはじめとするサーバ向けプロセッサの新展開や、「Cortex-Aシリーズ」関連の新IPなどについて紹介する。 「SystemReady」でx86を全方位追撃するArm、高性能組み込み機器向けもカバー

「SystemReady」でx86を全方位追撃するArm、高性能組み込み機器向けもカバー

Armが開催した年次イベント「Arm DevSummit 2020」の発表内容をピックアップする形で同社の最新動向について報告する本連載。今回は、「Cortex-A」ベースマシンのPC化を目指す「Project Cassini」と、それを具体化した「SystemReady」について紹介する。 Armのセキュリティ認証「PSA Certified」をリッチOSに広げる「PARSEC」とは

Armのセキュリティ認証「PSA Certified」をリッチOSに広げる「PARSEC」とは

Armが開催した年次イベント「Arm DevSummit 2020」の発表内容をピックアップする形で同社の最新動向について報告する本連載。今回は、「PARSEC」と「PSA Certified」を中心としたセキュリティ周りのアップデートについて紹介する。 Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

2019年10月6〜8日にかけてArmが年次イベント「Arm TechCon 2019」を開催した。本連載では、同イベントの発表内容をピックアップする形で同社の最新動向について報告する。まずは、Armのこれまでの方針を大転換することとなった、ユーザーに独自命令を組み込むことを許す「Custom Instruction」について紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク