“GPUのNVIDIA”がCPU製品「Grace」を投入、スパコンのAI性能が10倍に:GTC 2021 基調講演

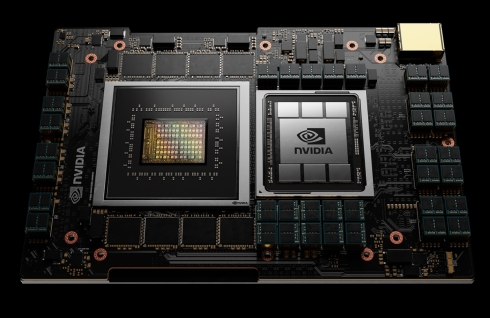

NVIDIAは、オンラインで開催中のユーザーイベント「GTC 2021」の基調講演において、巨大AIモデルやHPCのワークロードを処理するデータセンター向けのCPU「Grace」を発表した。Armの次世代サーバ向けプロセッサコアを搭載するGraceなどを用いたAIシステムは、x86ベースのCPUを用いる既存のAIシステムと比べて大幅な性能向上を実現するという。

NVIDIAは2021年4月12日(現地時間)、オンラインで開催中のユーザーイベント「GTC(GPU Technology Conference) 2021」(開催期間:同年4月12〜16日)の基調講演において、巨大AI(人工知能)モデルやHPCのワークロードを処理するデータセンター向けのCPU「Grace」を発表した。Armの次世代サーバ向けプロセッサコアを搭載するGrace、NVIDIAのGPUとインターコネクト技術「NVLink」、次世代メモリのLPDDR5xを組み合わせるなどしたAIシステムは、x86ベースのCPUを用いる既存のAIシステムと比べて大幅な性能向上を実現するという。

基調講演に登壇したNVIDIA CEOのジェンスン・フアン(Jensen Huang)氏は「AI技術が進化する中で、取り扱うAIモデルは大規模化している。それら巨大AIモデルの大量のデータをコンピュータシステムで処理する上で、データセンターのさまざまな用途に対応してきたx86ベースのシステムがボトルネックになりつつある」と語る。

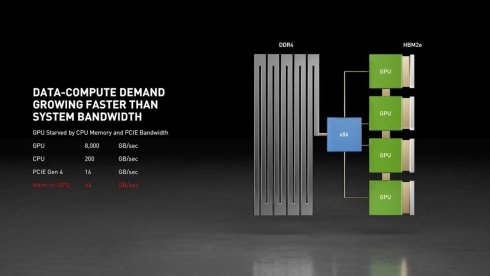

フアン氏がボトルネックと指摘するのは、x86ベースシステムにおける帯域幅の問題だ。NVIDIAが市販しているx86ベースのDGXのシステム(1CPU分)を例にとると、AI処理の中核を担う4つのGPUは、それぞれが2TB/sで動作する超高速メモリのHBM2eと接続されており、総計で8TB/sもの帯域幅を持つ。一方、メインメモリであるDDR4とCPUの間の帯域幅は200GB/sにすぎない。もしCPUとメモリ間の帯域幅を、チャネル数を増やすことで広げても、CPUとGPU間の接続がPCI-Expressなので、最新のGen4でも1レーン当たりの帯域幅が16GB/sとなり、メモリとGPU間の帯域幅は64GB/sにとどまってしまう。「大量のデータを処理するためにシステムが持つ全てのメモリを有効活用するには、このボトルネックとなっている帯域幅を広げる必要がある」(フアン氏)。

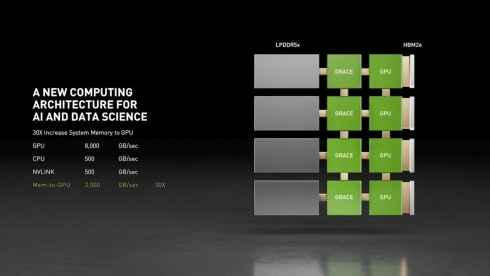

メモリとGPU間の帯域幅を大幅に拡大するべくNVIDIAが開発を進めているのがGraceである。Graceを用いるシステムでは、CPUとメモリ、CPUとGPU、CPUとCPUの間をNVLinkで接続することでそれぞれ500GB/sの帯域幅を確保する。これにより、メモリとGPU間の帯域幅は従来比で30倍となる2TB/sを実現できるというわけだ。

また、Graceに採用する次世代サーバ向けプロセッサコア(次世代アーキテクチャの「Armv9」ベースとみられる)により、CPU性能の大幅な向上も見込んでいる。現状のDGXのCPUは、AMDの「EPYC 7742」をデュアル構成で搭載しており、CPU性能を示すSPECintは450である。これに対して、Graceの1CPU当たりのSPECintは300で、8CPU構成となるDGXライクなシステムのSPECintは2400に達する。

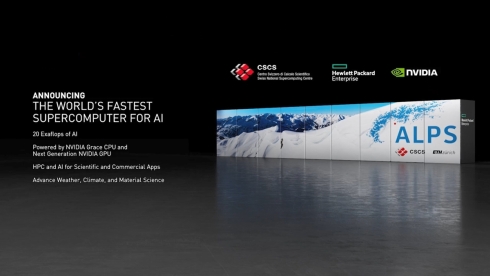

なお、スイス国立コンピューティングセンター(CSCS)は、このGraceとNVIDIAの次世代GPUを搭載するスーパーコンピュータ「ALPS」を2023年に稼働させる計画だ。そのAI処理性能は、現在スパコンランキング1位の「富岳」の10倍以上となる20エクサFLOPSを想定している。Graceそのものの市場投入も、同時期となる2023年前半を予定している。

CPUがコンピューティングの3つ目の基礎技術に

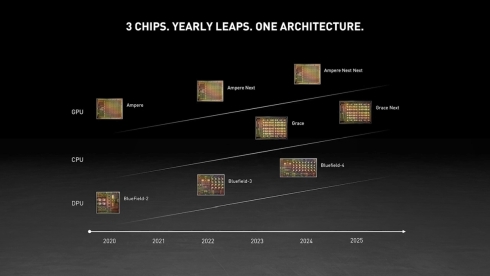

NVIDIAと言えばGPUのイメージが強いが、2020年10月に新たなカテゴリーの製品としてDPU(Data Processing Unit)の「BlueField」を発表している。今回のGTC 2021では、データ転送速度が400Gbpsとなる「BlueField-3」を2022年第1四半期に投入する方針を打ち出した。

その上でフアン氏は「パワフルなArmベースCPUのGraceは、コンピューティングの3つ目の基礎技術になる。今後、NVIDIAのデータセンター向けのロードマップは、GPU、CPU、DPUという3つのチップを、それぞれ2年ごとに進化させていくのが基本のリズムになる。x86プラットフォームに集中して技術を展開する年もあるだろう」と述べ、CPUアーキテクチャとしてArmだけでなくx86にもコミットし続ける姿勢を見せた。

関連記事

AIデータセンターの性能が20倍に、NVIDIAがAmpere世代のGPU「A100」を発表

AIデータセンターの性能が20倍に、NVIDIAがAmpere世代のGPU「A100」を発表

NVIDIA CEOのジェンスン・フアン氏は、YouTubeでオンデマンド配信した「GTC 2020」の基調講演において、新たなアーキテクチャ「Ampere」を採用したGPU「NVIDIA A100」を発表した。 NVIDIAがADAS用カメラもカバー、ロボタクシーは処理性能を6倍に

NVIDIAがADAS用カメラもカバー、ロボタクシーは処理性能を6倍に

NVIDIAは2020年5月14日(現地時間)、自動運転車向けのプラットフォーム「NVIDIA DRIVE」に次期型のSoC(System on Chip)「Orin」と新たなGPUアーキテクチャ「Ampere」を導入すると発表した。 NVIDIAがx86の縛りから解放へ、フアンCEOがArm進化に向けた3つの取り組みを発表

NVIDIAがx86の縛りから解放へ、フアンCEOがArm進化に向けた3つの取り組みを発表

NVIDIA CEOのジェンスン・フアン氏は、オンラインで開催中の年次カンファンレンス「GTC 2020」の基調講演において、2020年9月に買収を発表した半導体IPベンダー大手・Armとのパートナーシップの方向性について言及した。 NVIDIAによるArm買収、フアンCEOは「顧客や関連業界に多大な利益」と強調

NVIDIAによるArm買収、フアンCEOは「顧客や関連業界に多大な利益」と強調

NVIDIAとソフトバンクグループ(SBG)は、半導体IPベンダー大手のArmについて、NVIDIAがSBGとソフトバンク・ビジョン・ファンドから約400億米ドル(約4兆2400億円)で買収することで最終合意したと発表した。 NVIDIAのフアンCEOが日本で初披露、組み込みAI向け新製品「NVIDIA AGX」

NVIDIAのフアンCEOが日本で初披露、組み込みAI向け新製品「NVIDIA AGX」

NVIDIAのユーザーイベント「GTC Japan 2018」の初日に行われた基調講演に、創業者兼CEOのジェンスン・フアン氏が登壇。組み込みAIを可能にする新たな製品ラインアップ「NVIDIA AGX」のローンチを発表するとともに、国内の製造業がAI開発プラットフォームとしてNVIDIAのGPUや開発プラットフォームを広く採用していることをアピールした。 NVIDIAの第8世代GPU「Turing」は、レイトレーシングとAI向けで2つのコアを採用

NVIDIAの第8世代GPU「Turing」は、レイトレーシングとAI向けで2つのコアを採用

NVIDIAは、コンピュータグラフィックスのイベント「SIGGRAPH 2018」において、第8世代のGPUアーキテクチャ「Turing(チューリング)」と、Turingを搭載するプロ向けGPUボードの新製品「Quadro RTX 8000/6000/5000」を発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

NVIDIAのジェンスン・フアン氏。今回の基調講演も、コロナ禍での開催となった2020年5月からおなじみの“キッチンキーノート”スタイル

NVIDIAのジェンスン・フアン氏。今回の基調講演も、コロナ禍での開催となった2020年5月からおなじみの“キッチンキーノート”スタイル