IntelとAMDを超えたArmのサーバ向けプロセッサ、実はソフトバンクのおかげ?:Arm最新動向報告(11)(2/3 ページ)

「Cortex-A15」から10年かけてサーバ市場を狙えるIPを手に入れる

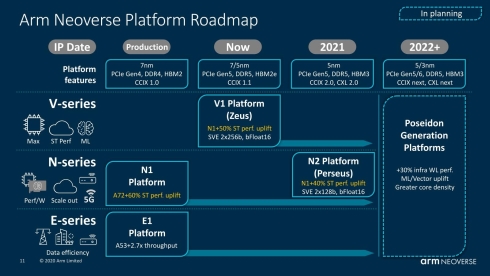

そして2020年9月の段階で、Vシリーズの最初のIPであるNeoverse V1を投入、2021年に入ってからはNeoverse N2を追加で投入することを発表した(図5)。

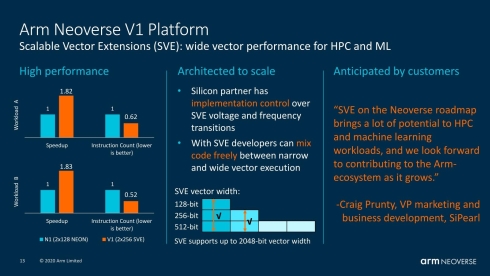

さて、このNeoverse V1であるが、ぶっちゃけ中身は「Cortex-X1」である。ただしサーバ向けに、NEON×2に替えて256ビット幅のSVE(Scalable Vector Extension)×2を実装している(多分他にも、ワークロードの負荷増大に対応して内部のバッファーの強化などもなされているだろう)。この結果として、通常のワークロードのみならず、数値演算などでも大きな性能向上が実現可能となっている(図6)。

図6 128ビットのSIMDエンジンを256ビット幅のSVEに変えただけでもかなりの性能改善になる。ちなみに図5に出てきた50%の性能改善はALU(Arithmetic and Logic Unit)周りの性能の話である(クリックで拡大)

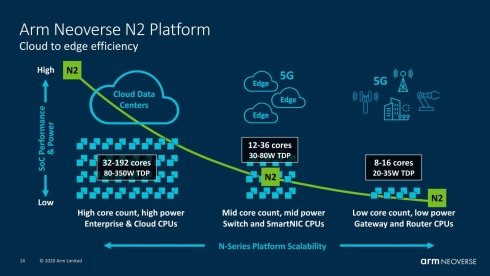

図6 128ビットのSIMDエンジンを256ビット幅のSVEに変えただけでもかなりの性能改善になる。ちなみに図5に出てきた50%の性能改善はALU(Arithmetic and Logic Unit)周りの性能の話である(クリックで拡大)一方のNeoverse N2は、性能向上ももちろんあるが(こちらは「Cortex-A78」がベース)、それよりもスケーラビリティを高める方にかじを切った(図7)。SVEが128ビット幅に抑えられているのも、個々のコアの性能を引き上げるよりは、全体として高い性能を発揮させるためには消費電力を控えめにした方が有利であり、SVEを128ビット幅に抑えることもこの一環と考えられる。SVEの場合、(図6にもちょっとあるが)128〜2048ビットまでサイズを可変できるが、プログラムそのものはSVEのベクターの幅にかかわらず共通である。そのためにこうした芸当ができることになる。

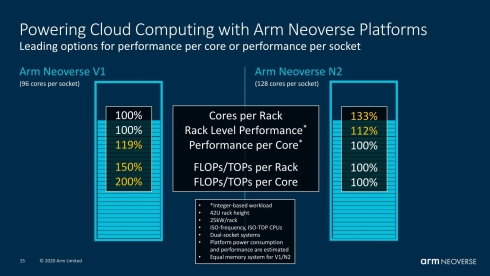

このNeoverse V1とNeoverse N2の性能比較というか、スペック比較をしたのがこちら(図8)。先ほどの図3と同様に、ラック当たりの消費電力を25kWに抑えるとすると、コアの数はNeoverse N2が3割大きく、ラック全体での処理性能はNeoverse N2が12%高い。その一方、コア当たりの性能はNeoverse V1が19%高い。このため、スケールアウトしやすいアプリケーションはNeoverse N2に、させにくいアプリケーションはNeoverse V1に任せればそれぞれ最大のパフォーマンスを得られる、ということになる。

図8 96cores/Socketとか128cores/Socketとか言っている時点で、既に想定されるプロセスは5nm世代と考えられる(7nm世代だと64core前後が限界だろう)(クリックで拡大)

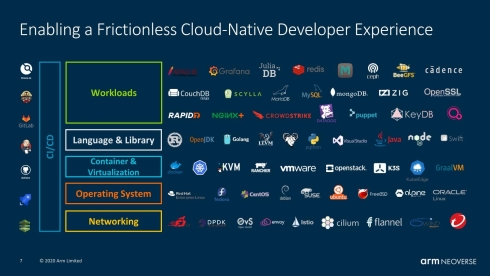

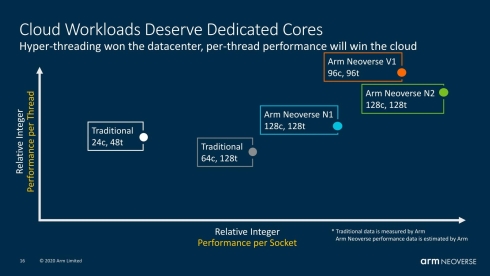

図8 96cores/Socketとか128cores/Socketとか言っている時点で、既に想定されるプロセスは5nm世代と考えられる(7nm世代だと64core前後が限界だろう)(クリックで拡大)興味深いのは、この世代で“Traditional 24c/48t”だけでなく“Traditional 64c/128t”も上回る性能が出せる、としていることだ(図9)。ここで24c/48t(24コア、48スレッド)はIntelの「Xeon Gold 8268」、64c/128tはAMDの「EPYC 7742」を想定している。つまり、やっと性能面ではXeonやEPYCに十分けんかを売れるだけの性能がこの世代で実現できる、としているわけだ。サーバ向けという言葉を初めて明確に出した「Cortex-A15」の登場から10年かけて、やっとArmは本気でサーバ市場を狙えるIPを手にしたわけだ。もちろんIPだけでサーバ市場が狙えるわけもなく、それもあってソフトウェアエコシステムへの対応も余念がない(図10)。

図9 横軸はソケット当たりの整数演算性能、縦軸はスレッド当たりの整数演算性能である。つまりNeoverse V1やN2は、XeonやEPYCをはるかに上回る整数演算性能を実現できるとしているわけだ(クリックで拡大)

図9 横軸はソケット当たりの整数演算性能、縦軸はスレッド当たりの整数演算性能である。つまりNeoverse V1やN2は、XeonやEPYCをはるかに上回る整数演算性能を実現できるとしているわけだ(クリックで拡大)いまさらながら思うが、この一連の流れはここ数年で急速に立ち上がった。要するにソフトバンクによるArm買収によって、こうしたエコシステム構築にこれまで以上にコストをかけられるようになった結果、である。その意味ではソフトバンクによるArm買収そのものは、決して悪い話だけではなかったと思う。

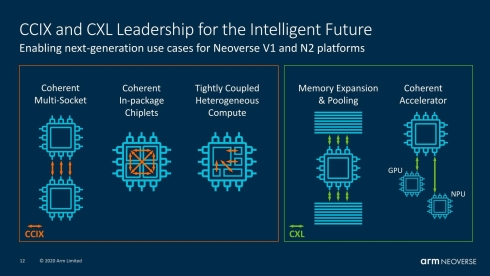

余談であるが、2020年に入ってNeoverseのインターコネクト関連ロードマップに少し変化が出てきた。2019年までのロードマップでは、自社のインターコネクト(CMN-600)にCCIX(Cache Coherent Interface for Accelerators)を組み合わせるという話で、それは現在も変わっていないのだが、単純なアクセラレータやメモリプールにはCXL(Compute Express Link)を利用することになった(図11)。

なぜ? というのは簡単で、CCIXは双方向のキャッシュコヒーレンシを提供でき、チップ間接続やダイ間接続には適当ではあるのだが、その分相対的に重いし実装コストも上がる。単純なGPUやNPUの接続にはCXLのような、片方向のキャッシュコヒーレンシを提供するもので十分という見極めができたのだろう。

加えてCXLがオープンスタンダードになり、実際最近リリースされたCXL 2.0はCXLコンソーシアム内できちんと仕様策定作業が行われるようになった。生い立ちこそIntel独自規格であったが、既に業界標準規格になっている。今後は、例えばマルチコア技術「DynamIQ」のACP(Accelerator Coherency Port)ポートの先にCXLでアクセラレータがつながる、なんてケースが出てくるかもしれない。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- ドローンやロボット向けの高性能で軽量なVLMを開発、8Bと2Bの2モデルを展開

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- ドライブレコーダーの録画時間を最大10倍に延長する動画ソリューション

- IoT向けネットワークサービスを活用しプリントシール機の安全基盤を検証

コーナーリンク