HDLを知らなくてもFPGAの力を引き出せる、インテルが無償のOpenCL開発環境:組み込み開発ニュース(1/2 ページ)

日本アルテラは、FPGAでOpenCLを扱うためのソフトウェア開発環境「Intel FPGA SDK for OpenCL」の最新バージョン「17.1」について説明。従来のコマンドラインベースのツールから、GUIを用いた統合開発環境となるとともに、新たに高速のエミュレータとコンパイラが加わった。

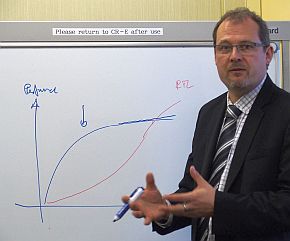

インテルのバンハード・フリーベ氏。ホワイトボードに書いているグラフは、横軸が開発期間、縦軸が性能。OpenCLを用いた開発(青色の線)は早期に性能を高められるのに対して、HDLを用いた開発(赤色の線)は性能向上に時間がかかる。ただし、最終的な性能については、最適化をつきつめられるHDLの方が高くなる(クリックで拡大)

インテルのバンハード・フリーベ氏。ホワイトボードに書いているグラフは、横軸が開発期間、縦軸が性能。OpenCLを用いた開発(青色の線)は早期に性能を高められるのに対して、HDLを用いた開発(赤色の線)は性能向上に時間がかかる。ただし、最終的な性能については、最適化をつきつめられるHDLの方が高くなる(クリックで拡大)日本アルテラは2018年1月22日、東京都内で会見を開き、2017年11月にインテル(Intel)がリリースしたFPGAでOpenCLを扱うためのソフトウェア開発環境「Intel FPGA SDK for OpenCL」の最新バージョン「17.1」について説明した。従来のコマンドラインベースのツールから、GUIを用いたIDE(統合開発環境)となるとともに、新たに高速のエミュレータとコンパイラが加わったことが特徴。さらに「17.0までは有償だったが、17.1からは無償になる」(日本アルテラ)という。

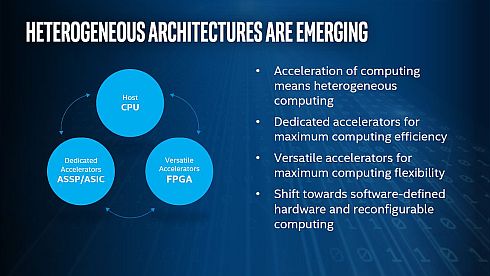

2016年1月にFPGAベンダーのアルテラ(Altera)を買収したインテルは、同社が目指すデータカンパニーに向けた取り組みの中で今後広く求められるであろう「ヘテロジニアスコンピューティング」において、FPGAが重要な役割を果たすとみている。インテル米国本社 プログラマブル・ソリューションズ事業本部 FPGAソフトウェア・ソリューション担当シニア・ディレクターのバンハード・フリーベ(Bernhard Friebe)氏は「ヘテロジニアスコンピューティングでは、インテルが得意とするCPUの他、専用アクセラレーターとなるASIC/ASSP、汎用アクセラレーターであるFPGAが混在することになる。特にFPGAは、ハードウェアアクセラレータでありながら再プログラミングが可能なため、ソフトウェアのように扱えることが大きな特徴になっている」と説明する。

とはいえ、FPGAをプログラミングするにはVerilogやVHDLなどのHDL(ハードウェア記述言語)に関する知識が必要になる。CやC++を扱う一般的なソフトウェア技術者にとって、HDLの習得はハードルが高いといわれおり、FPGAを扱いづらくする一因になっていた。この問題を解決するためにアルテラが早期から取り組んで来たのが、FPGAでOpenCLを活用するための標準化活動だ。

OpenCLは、ヘテロジニアスコンピューティングを扱うために、クロノス・グループ(Khronos Group)が標準化を進めているフレームワークである。アルテラは2010年にクロノス・グループに参加し、2012年にOpenCL向けソフトウェア開発キット(SDK)を発表するなどOpenCL関連の活動に注力してきた。「競合ベンダーに対して2年間のアドバンテージがある」(フリーベ氏)という。

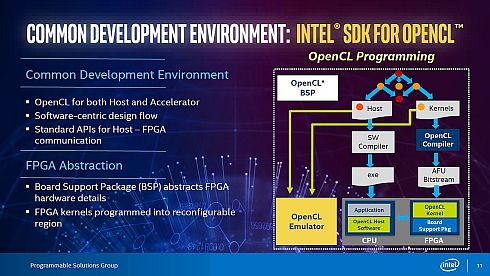

今回発表した「Intel FPGA SDK for OpenCL 17.1」は、これまで別々だったインテルとアルテラ両者のOpenCL対応ソフトウェア開発環境を統合したものとなる。インテル側で提供してきたGUIベースのIDEを基にして、アルテラ側でサポートしてきたOpenCLによるFPGAのプログラミングが可能になった。OpenCLでは、CPU側に「OpneCL Host Software」、FPGA側に「OpenCL Kernel」を組み込む必要がある。Intel FPGA SDK for OpenCL 17.1では、これらを1つのIDE上で、C++によるプログラミングで扱うことが可能だ。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク