富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も:人工知能ニュース(2/4 ページ)

» 2016年10月25日 15時00分 公開

[朴尚洙,MONOist]

2016年度内に基本最適化回路を公開へ

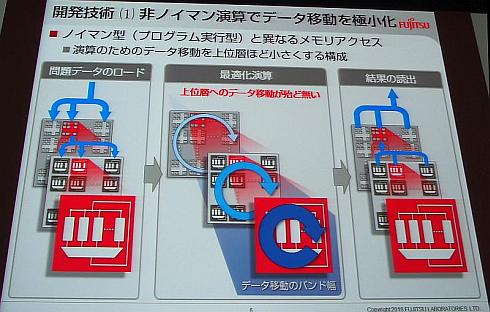

新アーキテクチャを実現するため開発した技術は2つある。1つは「非ノイマン演算でデータ移動を極小化」である。ノイマン型(プログラム実行型)と異なるメモリアクセスにより、演算のためのデータ移動を上位層ほど小さくする構成とした。

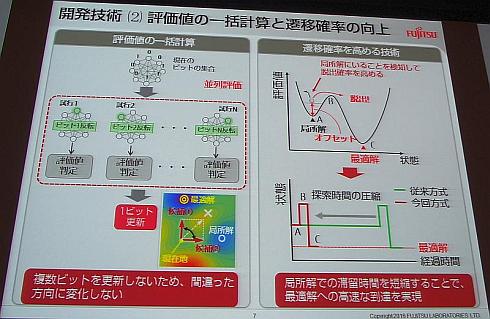

もう1つは「評価値の一括計算と遷移確率の向上」である。複数ある次の状態の候補に対するそれぞれの評価結果の値を一括して並列計算することにより、次の状態を見つけ出す確率を向上させる「評価値の一括計算」と、探索の途中で局所的な解にたどり着いてこう着状態になった場合に、これを検知して脱出確率を高めるための評価値に一定値を繰り返し加えることで次の状態に移行しやすくする「遷移確率の向上」により、高速に最適な解を求めることができる。

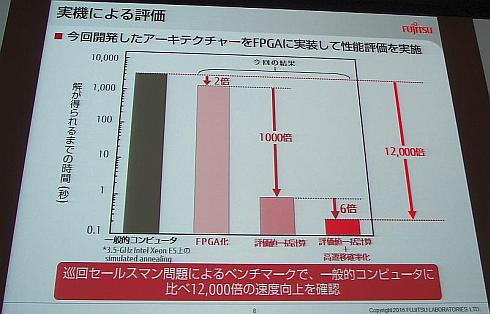

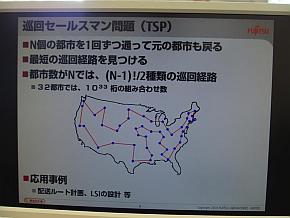

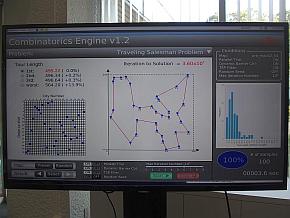

今回開発したアーキテクチャをミドルレンジのFPGAに実装して性能評価を実施した。組み合わせ最適化問題の代表例である「巡回セールスマン問題」によるベンチマークで、FPGAへの実装で2倍、評価値の一括計算で1000倍、遷移確率の向上で6倍の効果が得られたという。

今回の成果は基本最適化回路によって実現したものだ。今後は、複数の基本最適化回路を集積化するとともに上位の並列化を行い、100万倍の速度の達成を目指す。また、2016年度内に基本最適化回路を公開することでアプリケーション開発の促進も図る。

その上で、2018年度までに、実社会の問題が適用できる規模である10万ビットから100万ビットの計算システムを試作し、実用化に向けて実証を進めて行く予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

Special SitePR

コーナーリンク

あなたにおすすめの記事PR