FPGAの内蔵温度センサーから値を得る:MAX 10 FPGAで学ぶFPGA開発入門(13)(3/6 ページ)

ALTPLLの利用

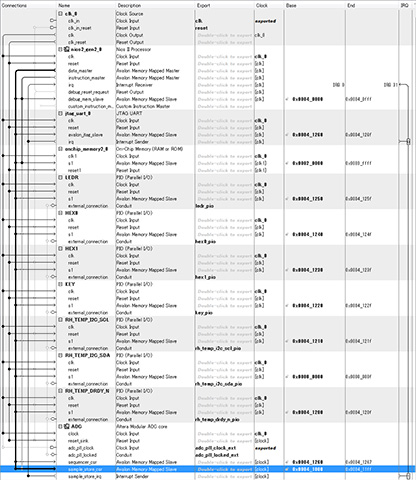

- 各コンポーネント同士を接続し、また“System” → “Assign Base Address”を行ってアドレス重複を解消する。

- ここまで終了したら、“TEMP_LED2_QSYS”という名前を付けて保存し、その後にGenerate HDLを行って終了する

- Quartus IIに戻り、TEMP_LED2_QSYS/synthesisの下にあるTEMP_LED2_QSYS.qipをプロジェクトに追加

- TEMP_LED2.vを編集……の前に、もう1つ追加するものがある。

前回のList1を見てもらうと分かるのだが、TerasicのSystem Builderを使うと無条件で50MHzのClock信号(MAX10_CLK1_50 / MAX10_CLK2_50 / MAX10_CLK3_50)と、それとは別にADC用に10MHzのクロック信号(ADC_CLK_10)が用意される。

MAX 10のADCは10/20/40/80MHzのクロック信号入力が想定されており、CPUの50MHz信号をそのまま入れることは不可能。そこで、このADC_CLK_10をそのまま利用しようと思ったのだが、これがうまくうかない。そもそもTerasicのサイトを見ても、このADC_CLK_10の使い方が良く分からないありさまである。そこで素直に50MHzの信号から10MHzのクロック信号を生成することにした。

Photo07:一覧が1画面で入りきらなかったので、抜き出して表示。一応ADCからCPUに割り込みを掛けられるようにIRQも接続している(これを接続しなくてもGenerate HDLはできるもが、Warningが出るので)

Photo07:一覧が1画面で入りきらなかったので、抜き出して表示。一応ADCからCPUに割り込みを掛けられるようにIRQも接続している(これを接続しなくてもGenerate HDLはできるもが、Warningが出るので)このために利用できるのが、Alteraが提供するMegaFunctionの1つである「ALTPLL」である。

ということで、これを追加して利用できるようにする。

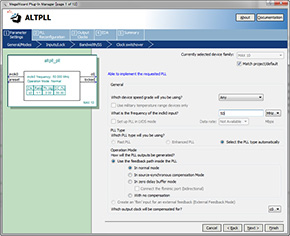

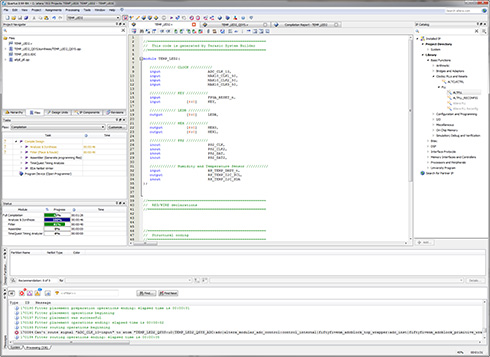

まずQuartus IIのIP Catalogから“Installed IP” → “Basic Functions” → “Clocks; PLL and Resets” → “PLL” → “ALTPLL”を選択する(Photo08)。するとファイル名の入力になるので、適当な名前を入れる(Photo09)。

Photo08:下のログに、ADC_CLK_10をADC Clockとして接続した場合のエラーが見えている。そもそもMAX 10の上に10MHzのClock Sourceがある訳ではなさそうで、ではこれは何のためにあるのか、が謎

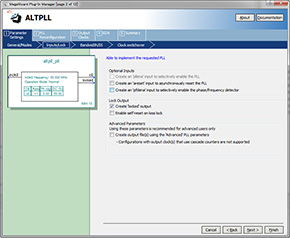

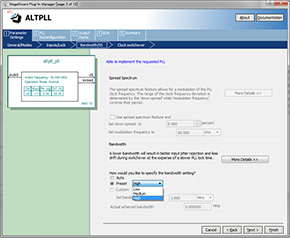

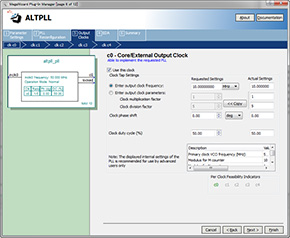

Photo08:下のログに、ADC_CLK_10をADC Clockとして接続した場合のエラーが見えている。そもそもMAX 10の上に10MHzのClock Sourceがある訳ではなさそうで、ではこれは何のためにあるのか、が謎するとPlug-in Managerが立ち上がるので、まず入力クロックに50MHzを指定する(Photo10)。次の“Input/Lock”タブは、Lock Outputにチェックを入れておくだけでいい(Photo11)。その次の“Bandwidth/SS”タブでは、“Bandwidth Setting”を“High”にする(Photo12)。

その次の“Clock switchover”は無視して、上の“Output Clock”タブを選択、ここの“clk c0”で出力を10MHzに設定する(Photo13)。最後に“Summary”タブで確認してから「Finish」を押すと、qipファイルを生成したことが示されるので、これをプロジェクトに追加する。

Photo13:いきなり“Requested Settings”には入力できないので、clock parameterで“multiplication factor”を1、“division factor”に5を入れてから“ << Copy ”ボタンを押すと10MHzに設定される

Photo13:いきなり“Requested Settings”には入力できないので、clock parameterで“multiplication factor”を1、“division factor”に5を入れてから“ << Copy ”ボタンを押すと10MHzに設定される関連記事

オンボードされた温湿度センサーからFPGAで値を得る

オンボードされた温湿度センサーからFPGAで値を得る

FPGA「MAX 10」搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、そこにはTI製の温湿度センサーも含まれる。サンプルプログラムを元に、オンボードされたデバイスの制御を試みる。 「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する

「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する

アルテラのFPGA「MAX 10」を搭載した開発ボード「MAX 10 NEEK」にはLEDやフラッシュメモリなどの各周辺機器が備えられている。今回はLEDを使ったストップウォッチを開発し、内蔵メモリから起動する。 「MAX 10 NEEK」に搭載されたDDR3メモリを使う

「MAX 10 NEEK」に搭載されたDDR3メモリを使う

MAX10搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、その中にはDDR3メモリも含まれる。ソフトコアCPU「Nios II」からの利用も含めて手順を紹介する。 「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。 周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

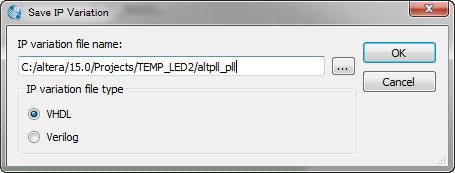

Photo09:当初"altpll"にしたら、さすがにそれは駄目だと怒られたのでaltpll_pllにしてみた。フォーマットはVHDLを選択する

Photo09:当初"altpll"にしたら、さすがにそれは駄目だと怒られたのでaltpll_pllにしてみた。フォーマットはVHDLを選択する