「MAX 10 FPGA」のテスト環境を構築する:MAX 10 FPGAで学ぶFPGA開発入門(2)(5/7 ページ)

» 2015年09月10日 07時00分 公開

[大原雄介,MONOist]

ちなみに、これで生成されたソースコードは以下「List1」になる。

ソースコードの説明はまた次回以降に説明するとして、これをこのままコンパイルしてファイルを生成、ダウンロードしてもLEDに変化はない。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Axelsys

// Engineer: Greg Miller

//

// Create Date: 11:21:08 08/21/2014

// Design Name: LED

// Module Name: LED_Verilog

// Project Name: Altera MAX10 Breakout Board

// Target Devices: 10M08SAE144C7G

// Tool versions: 14.0

// Description:

// LEDs, D1 through D5 will blink on for 1/2 second and off for 1/2 second.

// Clock is operating at 50MHz.

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module LED_Flash_all(

input clk,

output LED1,

output LED2,

output LED3,

output LED4,

output LED5

);

reg[15:0] div_cntr1;

reg[9:0] div_cntr2;

reg dec_cntr;

reg half_sec_pulse;

initial begin

div_cntr1 = 0;

div_cntr2 = 0;

dec_cntr = 0;

end

always@(posedge clk)

begin

div_cntr1 <= div_cntr1 + 1;

if (div_cntr1 == 0)

if (div_cntr2 == 762)

begin

div_cntr2 <= 0;

half_sec_pulse <= 1;

end

else

div_cntr2 <= div_cntr2 + 1;

else

half_sec_pulse <= 0;

if (half_sec_pulse == 1)

dec_cntr <= !dec_cntr;

end

assign LED1 = dec_cntr ;

assign LED2 = dec_cntr ;

assign LED3 = dec_cntr ;

assign LED4 = dec_cntr;

assign LED5 = dec_cntr ;

endmodule

*****

そこで最後の5行を書き換えてみた。

assign LED1 = dec_cntr ; assign LED2 = dec_cntr ; assign LED3 = dec_cntr ; assign LED4 = dec_cntr; assign LED5 = dec_cntr ;

から

assign LED1 = dec_cntr ; assign LED2 = !dec_cntr ; assign LED3 = dec_cntr ; assign LED4 = !dec_cntr; assign LED5 = dec_cntr ;

に変更してみた。

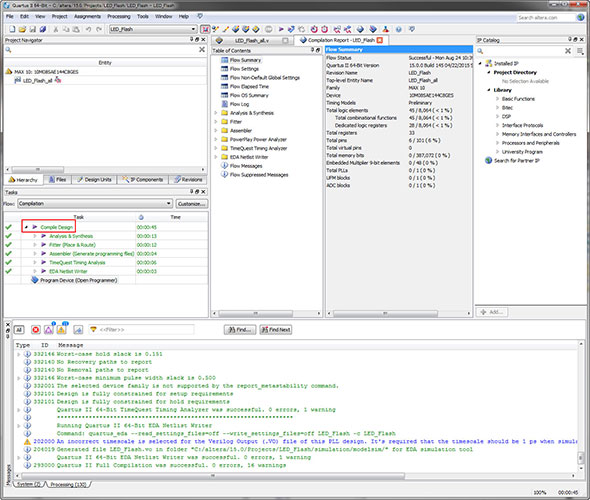

dec_cntrは0か1の値を取り、0ならLEDが消灯、1なら点灯する。そこでLED 1/3/5とLED 2/4に与える値を反転させることで、互い違いに点滅させようというものだ。この変更をQuartus IIの画面上で行ったら、やはり左側、Entityの下にある“Tasks”画面で“Compile Design”をクリックすると、問題がなければ数分(環境による:2回目以降は1分かからなかった)後にコンパイルが完了するはずだ(Photo25)。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

Special SitePR

コーナーリンク

あなたにおすすめの記事PR