第30回 インターポーザ:前田真一の最新実装技術あれこれ塾(3/4 ページ)

» 2015年03月17日 10時00分 公開

[前田真一,実装技術/MONOist]

3. インターポーザ基板

SoC(System on Chip)やMCPへの各種インタフェースやキャッシュメモリなど、1チップへの機能集積がICの微細化の以上に進んだ結果、チップの面積が増大し、と信号ピンが多くなりました。

これに合わせ、パッケージのピン数が増えると同時に、パッケージの小型化が望まれ、アレイ状のピン(ボール)を表面実装できるBGA(Ball Grid Array)パッケージが標準化されました(図13)。

さらにチップ面積とほぼ同じパッケージ面積のCSP(Chip Size BGA)も生まれました(図14)。

BGAパッケージでは多くのピンがパッケージ全面にアレイ状に配置されています。

多くのチップパッドからBGAのピン(ボール)への配線は非常に複雑になり、単純なリードフレームなどでは配線できなくなりました。複雑な配線では多層配線で、層を切り替え、配線を交差する必要があります。

ここで、インターポーザーに多層配線板を使う必要が出てきました。

この時点でチップの信号数は数百となり、しかもパッケージを小さくするためにはチップパッドのピッチは狭く、配線や配線切り替えのビアや信号配線をファイン化する必要があります。

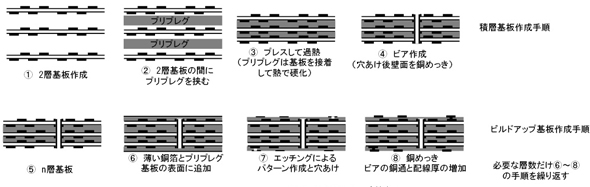

その頃、シーズとしてはちょうどビルドアップ基板の技術が開発されました(図15)。

薄くファイン化が可能なビルドアップ基板はインターポーザー基板としてよく使われています。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

Factory Automationの記事ランキング

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- ブラザー工業がパレットチェンジャー搭載シリーズの新モデル、主軸性能強化

- 複雑化/大型化するダイカスト部品の高速外観検査、NTNが新たな事業の柱模索

- 牧野フライスTOBに中止勧告、投資ファンド「大きな驚きをもって受け止め」

- 器用な指先を持つ手探りピック&プレースロボ、梱包作業の自動化で人間拡張

- データセンター向け需要に対応、大容量非常用発電システムの新工場建設へ

- ニデックがプレス機の新工場開設、生産能力倍増で工作機械とのクロスセル推進

- 滋賀本社に新工場、5面加工門形マシニングなど導入し大型部品の一貫生産強化

Special SitePR

コーナーリンク

あなたにおすすめの記事PR