第30回 インターポーザ:前田真一の最新実装技術あれこれ塾(2/4 ページ)

2. リードフレーム

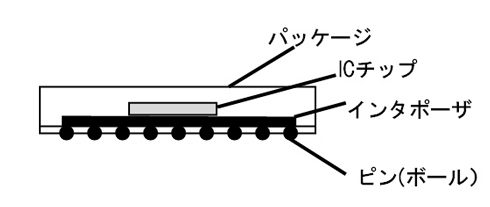

ピン数が少ないICのインターポーザにはリードフレームと呼ばれる部品が使われます。

これはICが出始め、形状が規格化された1970年代からずっと使われている部品です。

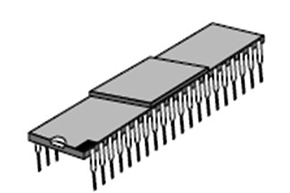

現在でもありますが、最初にICパッケージの形状が規格化されたときにはその形状はDIP(Dual Inline Package)と呼ばれる形状でした(図1)。

これは今でも使われていますが、パッケージの両側に2.54mm(10分の1inch)のピンピッチでスルーホールピンが出ているパッケージです(図2)。

このようなDIP型ICを代表に、多くのICにリードフレームが多く使われています。

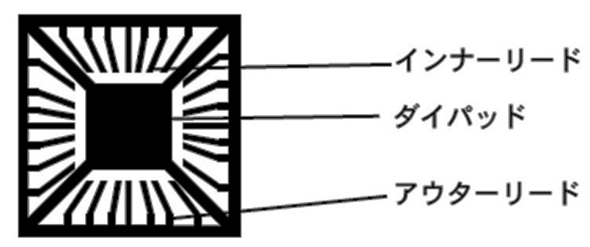

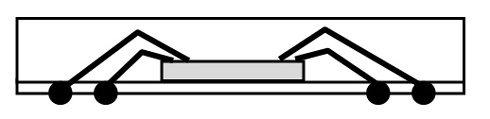

リードフレームは内側をICチップのパッド間隔、外側をICパッケージのピン間隔にした放射状の薄い金属の部品です(図3)。

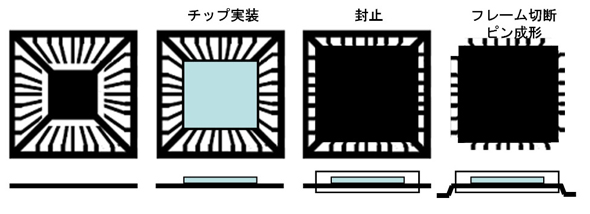

チップとリードフレームを接続した後、パッケージをプラスチックやセラミックで封止した後、封止から外に出た部分を折り曲げるとDIP ICが完成します(図4)。

ICの部品ピンはリードフレームの一部をそのまま使っています。

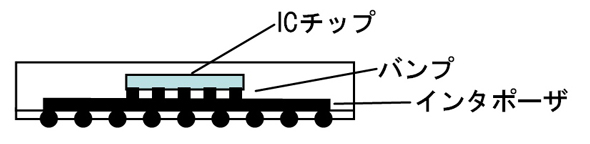

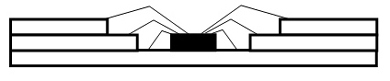

リードフレームとICチップを接続するためにはワイヤーボンディング(図5)やバンプによる直接接続が使われます(図6)。

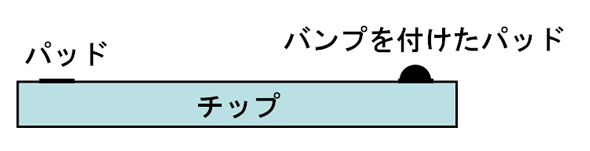

バンプ接続とは、あらかじめチップにバンプとよばれるはんだなどを盛り上げる処理を施したパッドを作っておき、接続する技術です(図7)。

ピン数が少ない場合にはDIPパッケージで問題はありませんでしたが、ピン数が多いICチップに対してはパッケージが大きくなりすぎてしまいます(図8)。

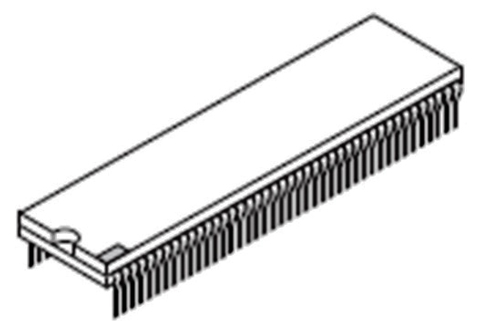

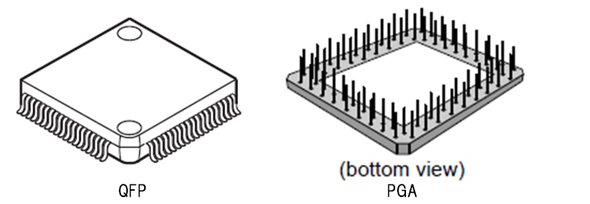

ピン数が大きくなるとピンをアレイ状に並べて小さな面積で多くのピンを並べ、パッケージが小さくなるようにする必要があります。ここで、規格化されたパッケージがパッケージの4方向にピンがあるQFP(Quad Fan-out Package)やアレイ状にピンを配列したPGA(Pin Grid Array)パッケージです(図9)。

QFPは表面実装タイプでリードフレームを使うことができます。

インターポーザとしては、リードフレームのかわりにポリイミドをはじめとするフィルムもインターポーザとして使われます。

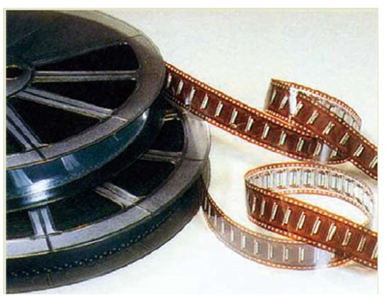

ポリイミドなどの薄くて柔らかいフイルムの特性を生かして、テープ状にしたインターポーザをチップに実装するTAB(Tape Automated Bonding)実装技術が使われます(図10)。

リードフレームや単層フイルムでは配線が交差したりチップのパッドより内側に部品ピンがあるようなアレイピン配置には対応できません(図11)。

薄いセラミックを積層するグリーンシートを使ったパッケージではキャビティ構造を使った多層配線を使うとピン配置の自由度が増します(図12)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク