解析実行エラーの原因と対策(その1):SPICEの仕組みとその活用設計(6)(2/3 ページ)

回路の特性を原因とする収束エラー

収束性に問題のある負荷の例(1):定電力負荷の場合

電子部品で構成される非線形負荷は、電圧を印加しなければ動作しませんから電流は流れません。つまり、強制的に原点を通る負荷特性になりますが、この範疇に属さない特殊な非線形素子の代表として、DC-DCコンバータなどを表す理想定電力負荷の解析を考えます。

なお、以下の手法は連載3回目で説明した非線形負荷の解析手法ですので、手順をお忘れの方はそちらの記事も参考にしてください。

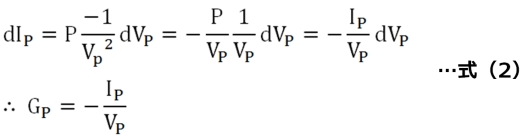

電圧・電流の関係は、定電力負荷なので式(1)で表されます。

ここで、Pは設定電力(W)、IPは負荷電流、VPは負荷電圧です。

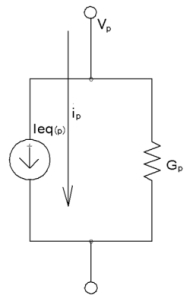

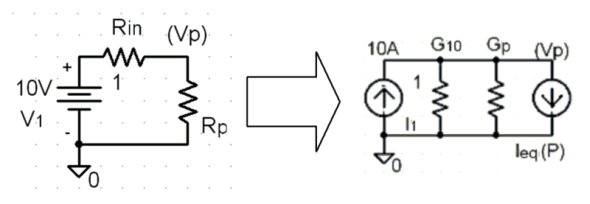

定電力負荷の接線コンダクタンスGPは式(2)から計算できるので、等価回路は図2のような構成で考えられます。そして、補正電流Ieq(P)は式(3)から計算できます。

また、式(2)からは、接線コンダクタンスGPが負になっていることが分かるので、従来の非線形負荷と振る舞いが異なることが予測できます。

計算例

開放電圧10V、電源内部抵抗Rin(1Ω)の電源から、この定電力負荷に10Wを与えます。

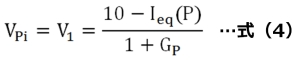

電圧源V1とRinを電流源I1とG10に置き換え、定電力負荷を図2の等価回路で表現すると、全体の回路図は図3となります。節点は1、0の2つだけですので、節点電圧V1は式(4)で求められます。

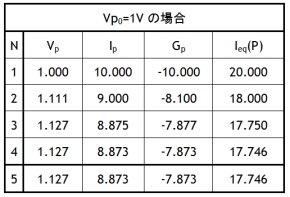

初期電圧Vp0=1Vとして実際に計算してみると、表1のように、5回目で収束します。

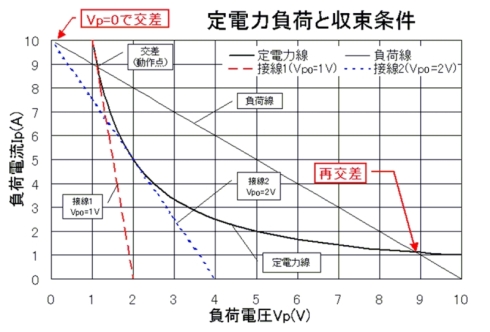

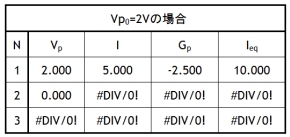

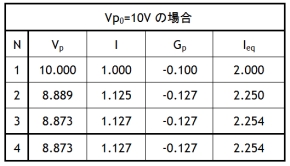

しかし、表2、表3に示すように、初期値の与え方によっては解が求まらない、あるいは別の解に収束する場合があります。このため、初期値についてはツール任せにはせず、意識を持って決めることが必要です。

これらの結果をグラフで示すと図4のようなイメージになります。

非線形負荷の場合、この他にも解が存在しないケースがあります。

例えば、電源内部抵抗Rinが大きい場合、電源から所定の電力を供給できません。この時には、いくら条件を調整しても正しい解は得られません。収束するか否か、設計者が事前に検討しておくことが必要になるケースがあるのです。

収束性に問題のある負荷の例(2):負荷特性が歪んでいる場合

詳細は専門書に譲りますが、時としてICの内部に意図しない寄生サイリスタなどが構造上作られてしまうことがあります。しかしながら、このサイリスタは意図したものではないので、正帰還作用が弱く、遷移状態への移行前電流の増加や、残留飽和電圧の増加が時々見られます。

バイポーラやCMOSのアナログICを開発する際には、この寄生サイリスタの影響を調べるために、周辺回路を含めてモデル化して解析しなければなりません。

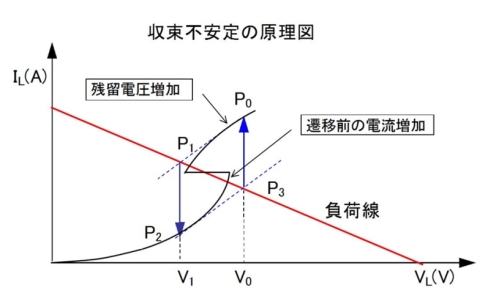

例えば、特性図が図5のような場合は、次のようなループを繰り返します。

- 初期値V0から動作点P0を算出

- P0の接線から交点P1を算出し、負荷電圧V1を得る。

- 負荷電圧V1から動作点P2を算出

- P2の接線から交点P3を算出し、負荷電圧V0に戻る

実際問題として完全にループに陥るわけではないのですが、収束に時間がかかる一因と成り得る事象です。

上記の2つの例から分かるように、負荷特性が遷移特性を含んでいたり、単調増加関数でなかったり、あるいは途中で曲率が反転している場合は、接線コンダクタンスが不連続、あるいは負になったり、負荷線と並行になって交点がなくなったりして、解析エラーが起こる原因になります。非線形負荷といえども、単調関数が好ましいのは言うまでもありません。また、回路の素子が、他の素子の寄生インダクタンスや寄生容量と共振し、不要な振動を持つ応答波形となって収束を妨げるケースもあります。

この様に、非線形負荷を用いた解析をスムースに行うには、負荷の特性がどのような特性になっているか、初期条件は適切なのか、といったことについて事前によく検討する必要があります。解析ツールは無敵ではないのです。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 軸受業界再編へNSKとNTNが経営統合に基本合意、両トップが語った危機感とは

- オムロンの制御機器事業が「再成長」に転換、M&Aで欧米顧客基盤を強化へ

- ファナックがGoogleと協業、AIエージェントでロボットを操作へ

- ファナックがNVIDIAと連携強化、物理エンジンで高精度デジタルツイン

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- 成功率90%超でコンテナ搬送、ヒューマノイドをシーメンス工場に試験導入

- 最大5台まで月2万円から、パナソニックコネクトのロボット制御基盤が拡充

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- データセンターが過去最高に貢献も、アマダは体制変更で新中計へ

- 高速ラインでの高精度な検査を可能にする、組み込みAIビジョンシステム

コーナーリンク

図2 定電力負荷

図2 定電力負荷

図3 全体の等価回路

図3 全体の等価回路

表1 成功した収束計算例

表1 成功した収束計算例 表2 失敗した収束計算例(Vp=0になる例)

表2 失敗した収束計算例(Vp=0になる例) 表3 別の解になった収束計算例

表3 別の解になった収束計算例