第1回 DDR4:前田真一の最新実装技術あれこれ塾(3/3 ページ)

5. DIMMの数

DDR4で信号が高速になり基板への実装が難しくなったことによっていちばん話題となっていることは、DIMMの接続数です。

DDR3ではDIMMが二つしか接続できないため、大きな制約があります。これが、DDR4ではDIMMは一つしか接続できなくなるのではないか、という議論が出ています。

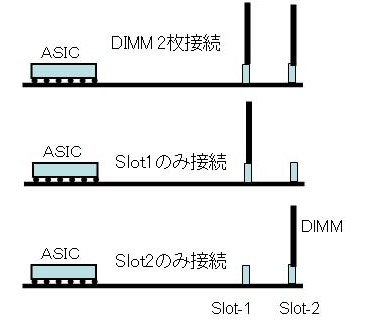

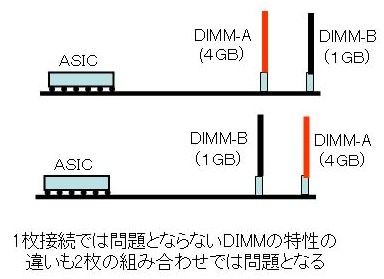

DIMMの数は純粋に伝送線路での波形品質の問題です。現在のDDR3でのDIMM二つ接続では、DIMMの接続は3通りが考えられます(図7)。二つのメモリの違いを入れると5通りになります(図8)。

この5通りすべての場合に対して、基板が完全に動作する必要があります。

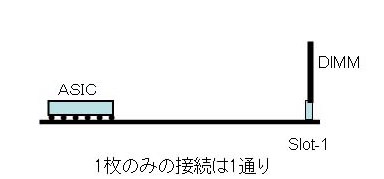

これは相当に難易度の高い伝送線路的な問題です。 これに対して、DIMMが一つだけの接続であれば1通りの組み合わせしかありません(図9)。こうなれば伝送線路信号の波形品質は格段に向上します。

しかし、DDR3のDIMM二つでもメモリ容量が不足で問題となっている時に、接続できるメモリを半分にするなどといったらDDR4は使えません。

もちろん、回路やコントローラを付加して接続できるDIMMの数を増やすことはできますが、これではコストが高くなり、また基板上の部品が多くなり、基板が大きくなってしまいます。特に、MPUやOSが64ビットに対応して32ビットOSの2GBの限界がなくなってから、PCのメモリ搭載量は急速に増大しています。このため、DDR4でも2DIMMはなんとしてもサポートしたいとのことで、検討もされています。

IBMのレポートでは、シミュレーションして2DIMMでも可能だと発表されていますが、今回のSamsung電子のサンプルなどを使って今後、DIMMの接続数については議論がなされるでしょう。

たとえば、2つのDIMMスロットには必ず特性の揃ったDIMMを両方のソケットに接続するなどの制限をつければ、DDR4でも2DIMMは実現できそうです。

しかし、たとえDDR4でDDR3と同じ2つのDIMM搭載をサポートしたとしてもこのままではメモリ不足はすぐにきます。それは、OSやソフトのメモリ要求に対して、チップの容量はDDRメモリではそれほど急激には上昇しないからです。

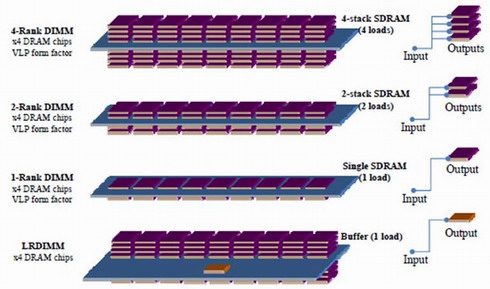

そこで、手っ取り早いDIMMの容量増加がJEDECで制定されています。それはメモリのスタック化です。すでにDDR3のDIMMでは2段のメモリスタックが実現されています。

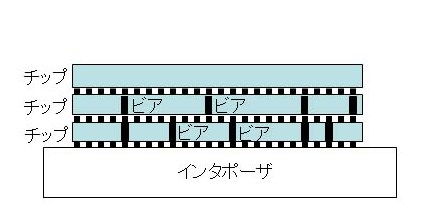

DDR4では、両面4段で8倍の容量のDIMMが検討されています。このスタック化はPoP(Package on Package)でもよいのですが、DIMMの厚さを考えたり、将来、デジタル家電や携帯にDDR4を使うことを考えると、ダイの積層実装が必然となるでしょう。

図10に、同じDesignConの発表で紹介されている積層実装によるDIMMを紹介します。

現在のスケジュールでは、2012年前半にDDR4の規格が決まれば2012年中にはサーバーなどハイエンドの装置に導入が始まり、その後、数年で広く使われるようになるでしょう。

しかし、TSV(図11)になるのか、他の方法でもスタックドICが実用化されなければ、DDR4が広く普及することは困難でしょう。

実装が新しい技術の普及を左右しているのです。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図7 DIMM2枚接続

図7 DIMM2枚接続 図8 DIMMのばらつき

図8 DIMMのばらつき 図9 DIMM1枚接続

図9 DIMM1枚接続 図10 DDRのStack

図10 DDRのStack 図11 TSV

図11 TSV