FPGAソリューションで新高速伝送規格の普及を後押し:電子機器 イベントレポート(30)(2/2 ページ)

ワークメモリを実質のエンドポイントと見なす

インタフェースIPコア「Z-coreシリーズ」で知られるインベンチュアの中村孝志氏が行った「FPGAで実現するUSB 3.0デバイス開発」も注目の技術セッションだった。

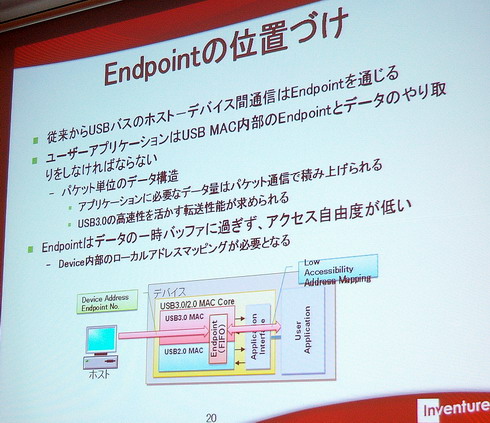

中村氏が指摘したのは「USBデバイスではエンドポイントの位置付けが重要になる」ということ。USBホストと直接通信するエンドポイントは通常、USBデバイスのMAC(Media Access Control)層に配置されるRAM領域だが、「FIFO(First In First Out)構造なのでアクセシビリティが低く、使い勝手が悪い」という。

そこで提案されたのは「MAC内エンドポイントは“一時的なFIFOバッファ”、ユーザーアプリケーションのワークメモリを“実質のエンドポイント”と見なす」という構造である。メモリマッピングされたワークメモリならアクセシビリティが高く、アプリケーションはパケットでなくデータ自体を扱えるようになるわけだ。

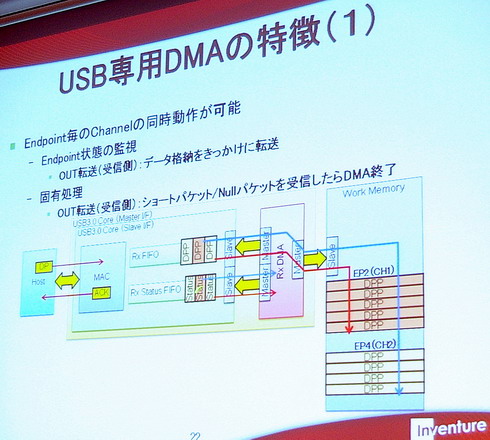

こうした構造では当然、MAC内のFIFOバッファとワークメモリ上のエンドポイントがCPUを介さず、DMA(Direct Memory Access)コントローラによりメモリ間通信を行う。中村氏は「各エンドポイントに対応する各DMAチャネルが同時動作することが必要」とした。

PHYチップとFPGA内実装MACをPIPE接続

続いて中村氏は、USB 3.0におけるPHY(Physical Layer)とMACのインタフェースについて、「PCI ExpressでPHY/MAC間の標準インタフェースとなっているPIPE(PHY Interface for the PCI Express)がUSB 3.0でも標準になるだろう」と指摘した。その上でUSB 3.0デバイスコントローラをFPGAに実装する上での留意点を次のように話した。

PIPEの最新版「PIPE 3.0」でもUSB 3.0に完全に対応しておらず、実装には工夫が要る。また、USB 3.0固有機能であるLFPS(Low Frequency Periodic signaling)も別途、論理的に実装する必要がある。USB 3.0で新規採用されたLFPSは、リンク開始前のトレーニング、ローパワーステートからの復帰などに使われる。8b/10bエンコード処理をバイパスしてLFPSの機能を実現するという。

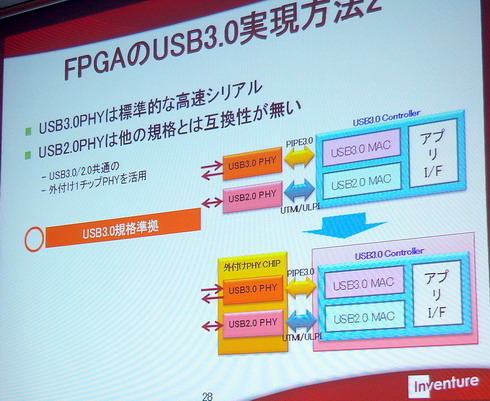

さらに中村氏からは、FPGAでUSB 3.0デバイスコントローラを実現する2つの方法が紹介された。1つは、USB 3.0のPHYにはFPGA内蔵SerDesマクロを使い、USB 2.0のPHYには外部チップを使うという方法。だが、この方法だと「スペクトラム拡散による最大偏差がUSB 3.0で規定された5000ppmを超える」という。もう1つの方法は、USB 2.0/3.0の両方に対応した外部チップを用い、それぞれの標準インタフェースでUSB 2.0/3.0 MACと接続するもの。これならUSB 3.0規格に準拠し、PHY/MACでIPコア組み合わせの自由度は高まるだろう。

その組み合わせの一例として、中村氏はインベンチュアとTEDが共同開発したUSB 3.0インタフェースを持つFPGAメザニンカードを紹介した。同製品はテキサス・インスツルメンツ(TI)のUSB 2.0/3.0共有PHYチップと、インベンチュアのUSB 3.0デバイスコントローラIPコア「Z-Core USB 3.0」を実装したSpartan-6 LX75Tを搭載する。「ターゲットのメインボードに接続すれば、即座にUSB 3.0インタフェースの評価が行える」(中村氏)。同製品は2011年4月より提供されるという。USB 3.0デバイスの評価・開発に役立ちそうだ。

以上、TEDプログラマブル・ソリューション 2011で興味深かった技術セッションをレポートした。ザイリンクス、TED、パートナーによるエコシステムは、組み込み業界で新インタフェース普及を強力に後押ししそうだ。

関連記事

MPUとの連携で存在感を強めるザイリンクスのFPGA

MPUとの連携で存在感を強めるザイリンクスのFPGA

東京エレクトロン デバイスは2011年2月16日、東京都内でプライベートカンファレンス「TEDプログラマブル・ソリューション 2011」を開催。パートナー企業とともに、FPGAに関する最新の技術・ソリューションを披露した。特に目を引いた「MPUとFPGAの連携」の部分をレポートする- 電子機器 イベントレポート

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- IoTとは何かを問いただすため、まずは薪ストーブに熱電対センサーを取り付ける

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 高温時のオン抵抗を3割削減、ロームの「第5世代SiC MOSFET」

- 電力を最大64%低減、エッジデバイスにも応用可能なモバイル向けプロセッサ

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

コーナーリンク

インベンチュアの中村孝志氏

インベンチュアの中村孝志氏 エンドポイントはFIFO構造のままでは使い勝手が悪い

エンドポイントはFIFO構造のままでは使い勝手が悪い エンドポイントとFIFOバッファのメモリ間通信をDMAで制御

エンドポイントとFIFOバッファのメモリ間通信をDMAで制御 FPGAに実装したUSB 3.0デバイスコントローラと外部PHYの接続

FPGAに実装したUSB 3.0デバイスコントローラと外部PHYの接続