ハードウェア設計にUMLを取り入れるメリット:SoC設計にモデリング手法を導入する(3)(2/3 ページ)

UMLモデリングの適用

次に、実際にUMLでモデリングを行うことで、仕様書へのUML適用の検討を行いました。以下では、各種のUML記述を利用して、実際のハードウェアモデルを検討していきます。

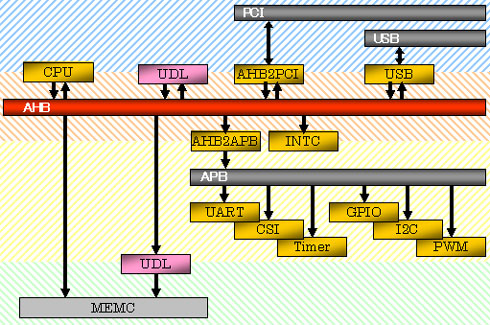

モデリング対象はAMBA* AHBバス

実際にモデリングを行うための題材として、AHBバスシステムを取り上げました。現在、SoC設計では頻繁に利用されるバスであり、グループのメンバーが共通に理解できることから、題材に選びました。(* AMBAはARM Limitedの登録商標です)

図2のようにSoC開発では、AHBバスを中心として各種バスやモジュールを接続した設計がよく行われます。図2では、PCI、USB、APBなどのバスがAHBバスにブリッジを介して接続されています。

ユースケース図

まず、バスのユースケースを簡単に書くことから始めました。当然ですが、バスの基本機能はデータを転送することです。それに加えて、バスに接続されるマスタが複数ある場合、各マスタから出されるバス権の要求を調停する機能が必要になります。これらをユースケースで簡単に表現すると以下のようになりました。

図3ではあまりに簡素で仕様が見えないため、仮のマスタ・スレーブの仕様を追加して、図4のように掘り下げました。マスタ・スレーブの仕様が具体的に明示され、図としてよりバス全体を理解しやすい図になりました。このように、ユースケース図を描くことで、視覚的な理解度を高めることができます。

しかし詳細化を進め過ぎて、バス権のアービタやアドレスデコーダなど、本来存在するものを表現するとさらに複雑になるので、どの粒度まで一度にユースケースとして表現するかは注意すべき点です。また、この図によって、すべての仕様を求めることはできないため、ほかのUML記述や非UMLの表現も援用すべきだと思います。

バス権を調停するアービタについては、別のユースケースとして記述しました(図5)。

図6は、マスタもシステムと見た場合のユースケースです。マスタの内部動作も見えてくるため、こちらの方がシステムとして具体的になります。

ユースケース図利用のまとめ

【利点】

- ハードウェアのユースケースを抽象度の高いレベルから表現できる

- ハードウェアのユースケースを視覚的に表現できる

【注意すべき点】

- 抽象度によっては具体的な要求仕様が見えない、または抽象度が低過ぎると具体的な要求仕様が見えない

- 詳細な仕様は見えない

シーケンス図

ハードウェア設計では図7のような波形を事象ごとに書いて、ハードウェア動作を表現するのが一般的です。このように実際の動作を波形で詳細に表すことは、設計において重要なことなのですが、知識が十分でない第三者がこのような波形ばかりの仕様書を読んで仕様を理解するのは難しいものがあります。また、書く側としては、このような波形をたくさん書くには多くの時間を費やし、書ける数にも限界があります。そのうえ、仕様変更があった場合、このような図を変更するのは手間がかかります。

図7 AHBアクセス(波形)

図7 AHBアクセス(波形)基本的なAHBリード/ライトアクセスを表現した波形。HWRITEがLowレベルの場合はリード、Highレベルの場合はライトアクセスとして動作する。AHBではバス権を保持しているマスタがアクセス情報を発行し(アドレスフェイズ)、それに応じて、スレーブが次のサイクル以降でデータのリード/ライトとアクセスに対する応答を行う(データフェイズ)

前節のユースケース図を基に、動作の流れを表現するシーケンス図を作成しました(図8、図9)。シーケンス図はモジュール間のメッセージ(データ)のシーケンシャルな動作を整理することができます。上記の波形と比べると、動作の流れは明快です。

しかし、クロックのサイクルが見えないため、詳細なタイミングまでは分かりません。詳細なタイミングを表現したい場合には、UMLのタイミング図で表現することも1つの手段です(今回はタイミング図の検討をしていません)。また、シーケンス図はパイプライン的なものや同じタイミングのメッセージ(データ)のやりとりを表現するには不向きです。

例えば図9では、ライトデータと応答が同じタイミングで発行されるのですが、シーケンス図のように時系列の流れを表現する図では、このようなタイミングを表現することは困難です。ハードウェア設計の場合、パイプライン的な並列動作の表現は避けられないため、シーケンス図は基本的な動作の理解や分析などの用途に限定されそうです。

図8 AHBシーケンス図(マスタのリードアクセス)

図8 AHBシーケンス図(マスタのリードアクセス)【動作】

1. マスタバス権を得るため、アービタにリクエストを発行する

2. アービタはバス権を発行する

3. マスタはアクセス情報(アドレス、サイズなど)をバスに発行する

4. バスがアドレスをデコードしアクセス情報がスレーブに到達する

5. スレーブはリードデータと応答を発行する

6. バスを介してリードデータと応答がマスタに到達する

図9 AHBシーケンス図(マスタのライトアクセス)

図9 AHBシーケンス図(マスタのライトアクセス)【動作】

1. マスタバス権を得るため、アービタにリクエストを発行する

2. アービタはバス権を発行する

3. マスタはアクセス情報(アドレス、サイズなど)をバスに発行する

4. バスがアドレスをデコードしアクセス情報がスレーブに到達する

5. スレーブはアクセスに対して、応答を返す

6. バスを介して応答がマスタに到達する

7. マスタはライトデータを発行する

8. バスを介してライトデータがスレーブに到達する

(実際は5〜8は同じタイミング)

シーケンス図利用のまとめ

【利点】

- シーケンシャルな動作の場合、波形で表現するよりも理解度が高い

- モジュール間のデータ(メッセージ)のやりとりが見える

【注意すべき点】

- パイプライン(並列)動作が表現しにくい

- 波形で書くようなクロックサイクルベースの詳細なタイミングは見えない(タイミング図で表現可能)

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

コーナーリンク

図2 AHBバスの構成例

図2 AHBバスの構成例 図3 AHBバスユースケース1

図3 AHBバスユースケース1

図5 アービタユースケース1

図5 アービタユースケース1 図6 アービタユースケース2

図6 アービタユースケース2