NVIDIA「Vera Rubin」は7つの新チップ、GroqのLPU追加でAIエージェント性能向上:人工知能ニュース(1/2 ページ)

NVIDIAは米国カリフォルニア州サンノゼで開催中のユーザーイベント「GTC 2026」の基調講演において、CPU「Vera」やGPU「Rubin」など新たなアーキテクチャを基にしたAIインフラの基盤「Vera Rubinプラットフォーム」を発表した。

NVIDIAは2026年3月16日(現地時間)、米国カリフォルニア州サンノゼで開催中のユーザーイベント「GTC(GPU Technology Conference) 2026」(開催期間:同年3月16〜19日)の基調講演において、CPU「Vera」やGPU「Rubin」など新たなアーキテクチャを基にしたAI(人工知能)インフラの基盤「Vera Rubinプラットフォーム」を発表した。

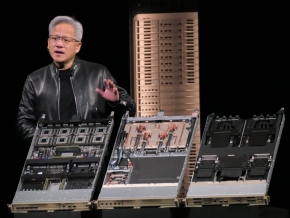

NVIDIA 創業者兼CEOのジェンスン・フアン(Jensen Huang)氏は「ブレークスルーを実現した7つのチップと、それらを基に構築した5つのラックシステムにより、全てのAI処理性能を向上する。特にAIエージェントについては、Vera Rubinプラットフォームの投入が大きな転換点になるだろう」と語る。

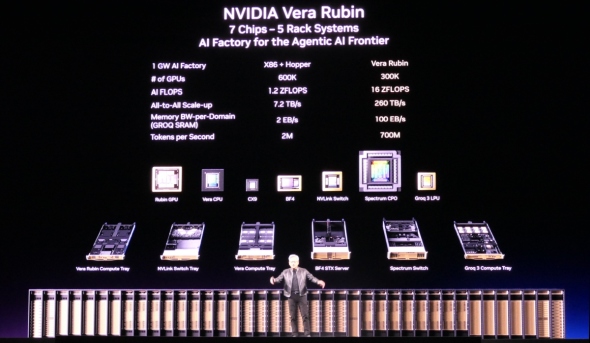

Vera Rubinプラットフォームは、AIインフラを構成する主要な7つのICを刷新することで大幅なAI処理性能向上を実現している。7つのうち、GPUのRubin、CPUのVera、サーバラック内の接続を担うスイッチICの「NVLink 6」、サーバラック間を接続するネットワークインタフェースICの「ConnectX-9」、データ処理を行うDPU(Data Processing Unit)の「BlueField-4」、データセンター間をつなぐイーサネットスイッチICの「Spectrum-6」の6つはこれまで発表されてきた。今回の発表では、2025年12月にライセンスを取得したばかりのグロック(Groq)の技術を用いたLPU(Language Processing Unit)「Groq 3 LPU」が新たに加わった。

新要素となるGroq 3 LPUは、AIサーバにおけるトークン生成を低遅延で行えることを特徴としている。NVIDIAが手掛けるGPUは、1チップ当たりのTPS(1秒当たりのトークン生成数)は高いものの、1ユーザー当たりのTPSと関わる遅延時間が大きいことが課題だった。一方、LPUは、低遅延のトークン生成に特化したプロセッサであり、1ユーザー当たり数千TPSも可能だ。ただし、そのためには多くのチップを使用する必要があり、GPUとは逆に1チップ当たりのTPSが低いことが課題になっていた。

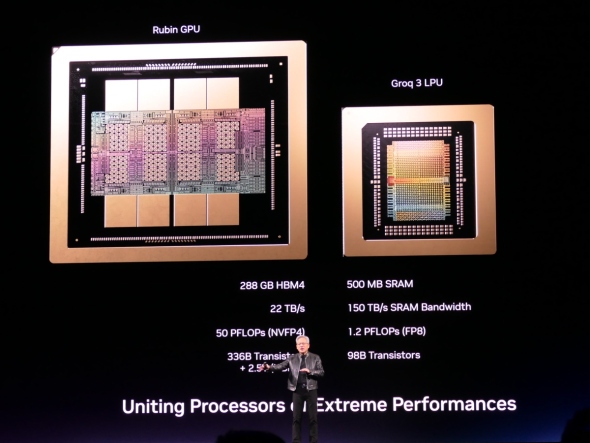

実際に、Rubinはメモリが容量288GBのHBM4、帯域幅が22TB/s、AI処理性能が50PFLOPS(NVFP4)、トランジスタ数が3360億個(+HBM4)。これに対し、Groq 3 LPUはメモリが容量500MBのSRAM、帯域幅が150TB/s、AI処理性能が1.2PFLOPS(FP8)、トランジスタ数が980億個となっており、Rubinと比べてメモリ容量が約500分の1ながら帯域幅は約7倍を達成している。まさにAI処理性能よりも低遅延のトークン生成を重視した設計となっているのだ。

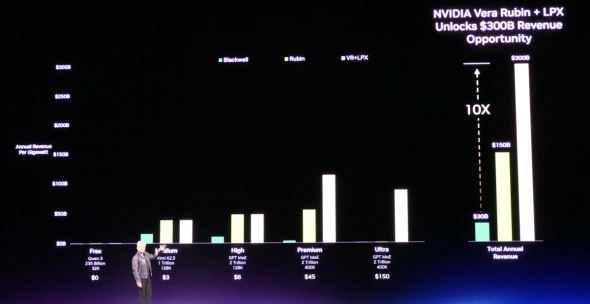

Vera Rubinプラットフォームは、RubinとGroq 3 LPUの組み合わせにより、高い1チップ当たりのTPSを維持しながら、低遅延のトークン生成により1ユーザー当たりのTPSも高いレベルで確保する狙いがある。1個のVeraと2個のRubinから構成される「NVIDIA Vera Rubin Superchip」を36枚搭載するラックシステム「Vera Rubin NVL72」と、Groq 3 LPUを256個組み込んだラックシステム「Groq 3 LPX」を組み合わせた場合、現行の「Blackwell GB300 NVL72」と比べると、同じ1ユーザー当たりのトークン生成数500TPSの条件で、消費電力1MW当たりのTPSは35倍になるという。また、1兆パラメーターのAIモデルを用いたサービスの収益性は、Blackwell GB300 NVL72単体で1米ドル、Vera Rubin NVL72単体で4米ドルなのに対し、Vera Rubin NVL72とGroq 3 LPXの組み合わせは10米ドルまで高められる。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク