インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ:モノづくり最前線レポート(5/5 ページ)

パッケージング技術の「EMIB」と「Foveros」も進化

半導体の性能向上では、微細化と関わる前工程に注目が集まりがちだが、加工精度が原子レベルまで行きついたオングストローム世代では、後工程に当たるパッケージング技術の進化がより重要になってくる。今回のIntel Acceleratedでは、2.5次元パッケージング技術の「EMIB(embedded multi-die interconnect bridge)」と、3次元パッケージング技術の「Foveros」「Foveros Omni」「Foveros Direct」も紹介された。

土岐氏は「これまでの半導体の真価は、集積度を高めて一つのモノリシックな半導体ダイにどんどん機能を詰め込んでいくというのが基本的な方向性だった。しかし、機能をさらに詰め込んでいくとそれに比例してダイ面積も大きくなり、併せて歩留まりも悪くなってしまう。こういったより多くの機能を搭載するニーズに応えるためマルチチップパッケージが活用されてきたが、モノリシックな半導体ダイの内部配線と比べて性能面で劣ることが課題になっていた」と語る。

EMIBは、パッケージの中に半導体ダイベースのブリッジを組み込むことで、マルチチップパッケージの課題を解決する技術だ。従来の一般的なパッケージと比べて、バンド幅が2倍、電力効率で4倍の性能を発揮するという。今後は、EMIBのバンプ(端子)間距離(ピッチ)を55μmから45μm、40μmと狭ピッチ化していく方針。

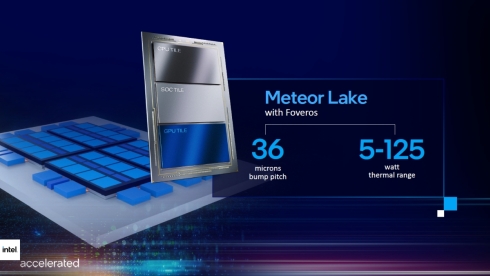

EMIBは2.5次元パッケージング技術とある通り、複数の半導体ダイを並べてつなげていくためのものだ。これに対してFoverosは、クライアントPC向けなどの消費電力でも実用的に利用できる3次元パッケージング技術となっている。Intel 4がComputeタイルに適用されるMeteor Lakeでは、これらEMIBとFoverosをフル活用することになる。バンプピッチはさらに狭ピッチ化して36μmとなり、消費電力は5〜125Wの範囲で対応できるという。

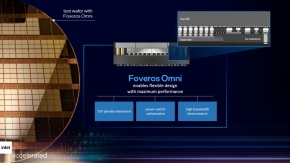

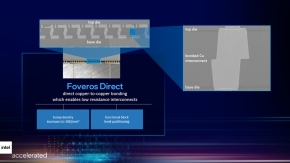

Foverosについては、さらに次世代となるFoveros Omni、次々世代となるFoveros Directも開発が進められている。Foveros Omniは、パッケージ内の上方に置かれるトップダイから基板に直接つながるTSV(貫通シリコンビア)を用いる構造になる。そして、Foveros Directでは、これまでパッケージ内部のダイとダイの接続に用いていたはんだボールに替えて、ダイ表面に作り込まれた銅電極同士で接続を行う。

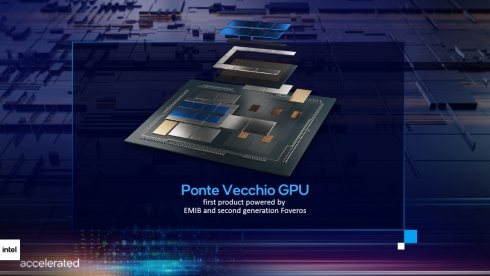

なお、現在開発が進められているGPUの「Ponte Vecchio」はEMIBとFoveros Omniを採用する最初の製品になる。

インテルのファウンドリーサービスをAWSとクアルコムが採用

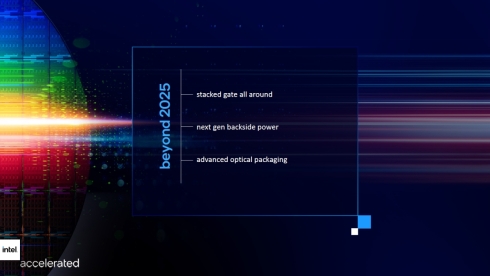

2025年以降の技術開発では、全周ゲート型トランジスタや裏面からの電源供給のさらなる進化を続けるとともに、パッケージング技術におけるシリコンフォトニクスの融合などが検討されている。

また、インテルのファウンドリーサービスであるIFSの顧客名も明らかになった。まず、IFSのパッケージングサービスではAWSがデータセンター向け半導体製品での採用を決めており、スマートフォン向けプロセッサで高シェアを占めるクアルコムがIntel 20Aの採用を表明している。

関連記事

新CEOの「IDM 2.0」がインテルを戒めから解き放つ、ファウンドリー事業にも本腰

新CEOの「IDM 2.0」がインテルを戒めから解き放つ、ファウンドリー事業にも本腰

インテルが、7nmプロセスの進捗状況や、ファウンドリー事業の立ち上げ、工場の建設計画などについて発表。2021年2月に新CEOに就任したパット・ゲルシンガー氏がグローバルWebキャストに登壇し、同社がこれまで堅持してきたIDM(垂直統合型デバイス製造)を大きく進化させる「IDM 2.0」のビジョンについて説明した。 10nm採用の第3世代「Xeon SP」はエッジでも展開、AI性能はNVIDIA「A100」の1.3倍

10nm採用の第3世代「Xeon SP」はエッジでも展開、AI性能はNVIDIA「A100」の1.3倍

インテル日本法人がデータセンター向けの「Xeonスケーラブル・プロセッサー(以下、Xeon SP)」の第3世代品を発表。10nmプロセスを採用することで、14nmプロセスの第2世代Xeon SPと比べて平均46%の性能向上を果たした。主な用途は、クラウド、エンタープライズ、HPC、5Gの他、IoTなどエッジでの利用も可能としている。 インテルがIoTエッジ向けプロセッサに10nmプロセスを採用、TSNや機能安全対応も

インテルがIoTエッジ向けプロセッサに10nmプロセスを採用、TSNや機能安全対応も

インテル(Intel)が産業機器などのIoTエッジ向けに10nmプロセスを採用したプロセッサ製品群を発表。低消費電力を特徴とする「Atom」の新たな製品ライアップとして「Intel Atom x6000Eシリーズ」を投入し、より性能を重視した用途向けには「第11世代 Core プロセッサ ファミリー」をIoTエッジ向けに最適化した製品を展開する。 インテルの新プロセッサ「Tiger Lake」、トランジスタやメタル改良で高性能化

インテルの新プロセッサ「Tiger Lake」、トランジスタやメタル改良で高性能化

インテルは2020年9月3日、報道関係者向けのプレスセミナーをオンライン開催し、動作周波数の向上と消費電力の削減を同時に達成する「SuperFinプロセステクノロジー」や、新グラフィック機能などを実装した第11世代インテル Core プロセッサ ファミリーを発表した。同プロセッサの開発コード名は「Tiger Lake」である。 インテルが5G基地局向けにAtomプロセッサを開発、ストラクチャードASICも投入

インテルが5G基地局向けにAtomプロセッサを開発、ストラクチャードASICも投入

インテルは5Gインフラ向けの新製品ポートフォリオを発表した。5G無線基地局向けのSoC「Intel Atom P5900 プロセッサ」など全4種類を発売する。 目がキラッキラッのインテル新CEOゲルシンガー氏には期待せざるを得ない

目がキラッキラッのインテル新CEOゲルシンガー氏には期待せざるを得ない

いやホントに目がキラッキラッなんですよ。これが。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク