膨大な組み合わせ最適化問題向けの大規模並列処理回路を開発:人工知能ニュース

東芝は、膨大な組み合わせパターンの最適化を行うための「シミュレーテッド分岐アルゴリズム」専用の大規模並列処理回路を開発した。金融取引や産業用ロボットなどの分野にSBアルゴリズムを適用することが可能となる。

東芝は2019年9月11日、膨大な組み合わせパターンの最適化を行うための「シミュレーテッド分岐アルゴリズム(SBアルゴリズム)」専用の大規模並列処理回路を開発したと発表した。同回路を搭載することで、金融取引や産業用ロボットなど、高速で良解を選び、反応することが必要な分野に、SBアルゴリズムを適用可能となる。

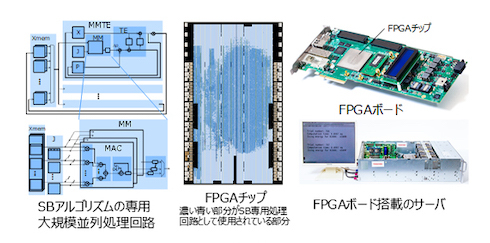

今回開発された回路は、専用でSBアルゴリズムをハードウェア処理する。空間並列化と時間並列化の回路手法により設計された大規模並列処理回路で、SBアルゴリズムに含まれる演算のうち同時刻に実行可能な演算を解析した結果に基づいている。

クロックサイクルごと、1ビットデータごとの最も細かいレベルでの回路最適化を施し、高速処理性能と省電力性能を両立した。

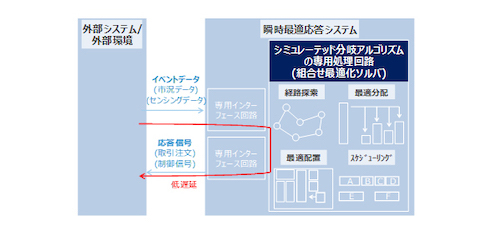

汎用プロセッサ上のソフトウェア処理の制御を必要とせず、0.001秒未満レベルで外部環境の変化を検知し、膨大な選択肢の中から良解を選ぶことが可能な瞬時最適応答システムを構築できる。

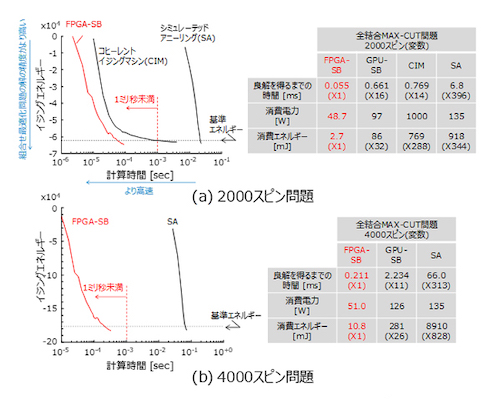

本回路は、冷凍機などの特殊な付帯設備なしに市販の再構成可能論理回路(FPGA)に実装可能だ。20nm世代のFPGAに実装した場合、従来同社が発表したFPGAの組み合わせ最適化問題を扱えるサイズと比べて4倍、速度では11倍、エネルギー効率では26倍の成果が得られた。

同社は今後、本回路を応用した実験機の研究開発を進め、2019年中の発表を目指すという。

関連記事

量子コンピュータとAI、先進技術における日本の最新動向と位置付け

量子コンピュータとAI、先進技術における日本の最新動向と位置付け

日本最大級の産学官連携イベント「イノベーション・ジャパン2019」(2019年8月29〜30日、東京ビッグサイト青海展示棟)において、科学技術振興機構(JST)事業セミナーで、JST研究開発戦略センター(CRDS)がAI技術および量子コンピュータ技術の最新動向について紹介した。 量子コンピュータで平均28%削減、OKIが製造現場の動線効率化で

量子コンピュータで平均28%削減、OKIが製造現場の動線効率化で

OKIとOKIデータは2019年9月5日、OKIデータのLED統括工場においてD-Waveの量子コンピュータを活用し作業員の動線効率化に成功したと発表した。半導体製造装置の最適配置により、作業員の移動距離を28%短縮できたという。 振動環境発電を最大化する磁石の配列を組み合わせ最適化で導出

振動環境発電を最大化する磁石の配列を組み合わせ最適化で導出

富士通研究所は、組み合わせ最適化問題を高速で解く次世代アーキテクチャ「デジタルアニーラ」を活用し、環境発電で使用する磁気デバイスの最適な設計解を求める技術を開発した。 組み合わせ最適化問題をAWSで高速処理、東芝デジタルが期間限定で無償公開

組み合わせ最適化問題をAWSで高速処理、東芝デジタルが期間限定で無償公開

東芝デジタルソリューションズは2019年7月17日、大規模組み合わせ最適化問題を高速に処理するソフトウェア「シミュレーテッド分岐マシン(Simulated Bifurcation Machine)」をAWS(アマゾンウェブサービス)のマーケットプレース上で公開したと発表した。2019年10月末までの期間限定で、PoC(概念検証)版として無償公開されている。 組み合わせ最適化問題を解決する新しいアナログニューラルネットワーク

組み合わせ最適化問題を解決する新しいアナログニューラルネットワーク

東京大学は、従来のデジタル計算技術に置き換わる可能性のあるアナログニューラルネットワークを発表した。実社会に存在する「組み合わせ最適化問題」を解き、電子回路に組み込むことで処理の高速化が期待される。 量子コンピューティングを製造現場へ、組み合わせ最適化の価値を訴えた富士通

量子コンピューティングを製造現場へ、組み合わせ最適化の価値を訴えた富士通

富士通は、ハノーバーメッセ2019(2019年4月1〜5日、ドイツ・ハノーバーメッセ)において、量子コンピューティング関連技術の1つで組み合わせ最適化問題に力を発揮する量子アニーリングを製造現場に適用する提案を行った。量子アニーリングの専用チップなども紹介し、先進の量子コンピューティング技術により、製造現場を最適化することを訴えた。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

開発したSB専用回路を応用した瞬時最適応答システム 出典:東芝

開発したSB専用回路を応用した瞬時最適応答システム 出典:東芝 開発したSB専用回路の専用回路とそのFPGA実装例 出典:東芝

開発したSB専用回路の専用回路とそのFPGA実装例 出典:東芝 開発した専用回路(FPGA-SB)の速度性能とエネルギー効率 出典:東芝

開発した専用回路(FPGA-SB)の速度性能とエネルギー効率 出典:東芝