Armのサーバ向け戦略十年の計は実を結ぶか、新プロセッサ「Neoverse」:Arm最新動向報告(2)(2/3 ページ)

初期の失敗にめげずサーバ向け製品をリリース

そんなわけで、下回りから次第にシェアを高めていったArmであるが、より上位のサーバ用プロセッサを諦めた訳ではもちろんない。実際、初期の失敗にもかかわらず、引き続き上位のサーバに向けた製品をリリースし続けた。

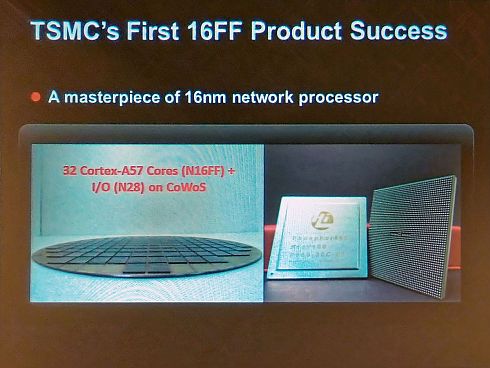

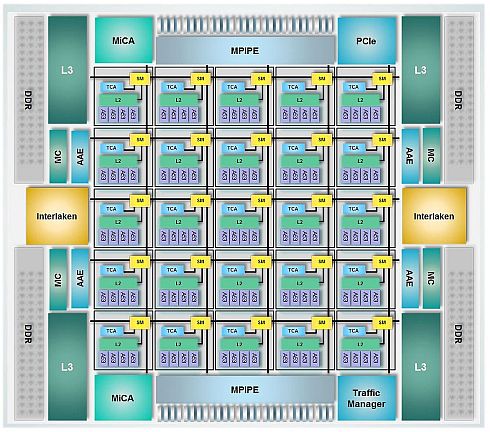

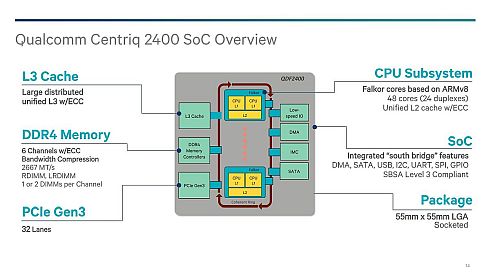

例えば、中国のHiSiliconは2014年9月、TSMCの16nm製造プロセス「16FF」(16FF+にあらず)を利用して32コアのCortex-A57を集積したサーバ向けチップを発表している(図3)。イスラエルのEZ-Chip(2016年にMellanoxにより買収)は2015年2月、100コアのCortex-A53を搭載したTile-MX100(図4)をリリース。そして2017年11月にQualcommは、独自開発の「Falkor CPU」を48コア集積したサーバ向けCPUとして「Centiq 2400」を発表している(図5)。

図3 2014年の「Arm TechCon」におけるTSMCのセッションより。最大2.6GHz駆動の「Cortex-A57」を32コア搭載した16FFのチップと、I/Oを集積した28nmプロセス製造のチップをCoWoSを利用して積層した構成(クリックで拡大)

図3 2014年の「Arm TechCon」におけるTSMCのセッションより。最大2.6GHz駆動の「Cortex-A57」を32コア搭載した16FFのチップと、I/Oを集積した28nmプロセス製造のチップをCoWoSを利用して積層した構成(クリックで拡大) 図4 「Tile-MX100」の構成図。もともとEZ-Chipは1999年に設立されたファブレス企業だが、2014年に米国のTileraというマルチコアプロセッサの極北を突っ走るメーカーを買収した結果、一気に多コア化に突き進んだ(クリックで拡大)

図4 「Tile-MX100」の構成図。もともとEZ-Chipは1999年に設立されたファブレス企業だが、2014年に米国のTileraというマルチコアプロセッサの極北を突っ走るメーカーを買収した結果、一気に多コア化に突き進んだ(クリックで拡大) 図5 これは2017年の「HotChips」におけるQualcommの発表資料より。Falkorは4命令同時デコード、8命令同時発行のOoO(Out of Order)実行プロセッサで、Arm v8A(AArch64のみ)対応となっている(クリックで拡大)

図5 これは2017年の「HotChips」におけるQualcommの発表資料より。Falkorは4命令同時デコード、8命令同時発行のOoO(Out of Order)実行プロセッサで、Arm v8A(AArch64のみ)対応となっている(クリックで拡大)Armサーバは、こうした多コア化が1つの特徴であり、それが故に(旧Tileraのインターコネクト技術を持つ)EZ-Chipとか、長らく独自でコアを開発してきたことで技術力を蓄積しているQualcommといったベンダーがArmサーバに名乗りを上げたというわけだ。しかし、さらに広範にArmサーバのマーケットを広げてゆくためには、こうした技術力の高いベンダーに任せるのではなく、コアそのものに加えてスケーラビリティの高いインターコネクトも同時にIPとして提供していく必要がある。

そこで、サーバ向けにカスタマイズしたCPU IP、それとサーバ向けのインターコネクトや周辺回路のIPを、Neoverseというブランドで投入することにしたというのは、要するにようやくArmをベースにサーバ市場に参入したいというベンダーが増えてきたことの現れ、として良いかと思う。

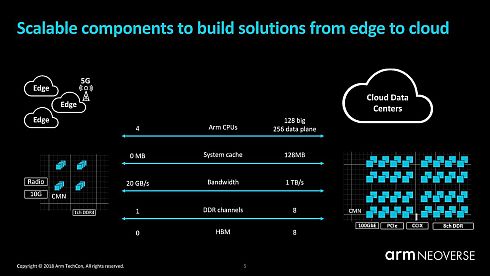

さてそのNeoverseであるが、構想としてはそれこそ4コアから128コアまでの広範なスケーラビリティが最大の特徴である(図6)。ローエンドはエッジ向け、ハイエンドはクラウドサービスまでがカバー範囲となる。

図6 もちろん256コアともなると、そもそも1つのチップで収めるのは現状でも難しい。しかし「Neoverse」そのものは、5nmやその先のプロセスも見据えた上で、この辺りまでのスケーラビリティを提供する、ということだ(クリックで拡大)

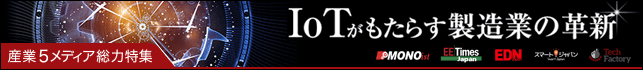

図6 もちろん256コアともなると、そもそも1つのチップで収めるのは現状でも難しい。しかし「Neoverse」そのものは、5nmやその先のプロセスも見据えた上で、この辺りまでのスケーラビリティを提供する、ということだ(クリックで拡大)まず、プロセッサというかプラットフォームであるが、現在出荷中のもの(2018年11月に発表があった、Annapurna labsがAWSのために製造した「Graviton Processor」がこの代表例)が「Cosmos Platform」、そして2019年1月の「CES 2019」でHuaweiが発表した「Kunpeng 920」が「Ares Platform」となる。

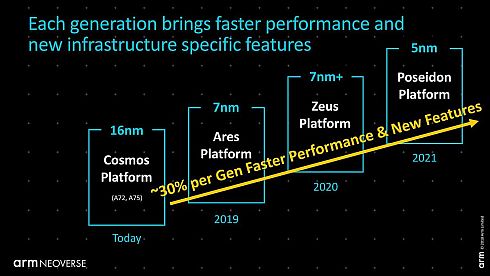

これに続き、2020年には「Zeus Platform」、5nm世代では「Poseidon Platform」が控えている(図7)。それぞれのプラットフォームの具体的な構成が図8で、世代毎にどんどん大規模になっていることが見てとれる。これらのうち、Cosmos Platformに関しては、3種類のSGI(System Guidance for Infrastructure)が既に提供中であることが明らかにされている。

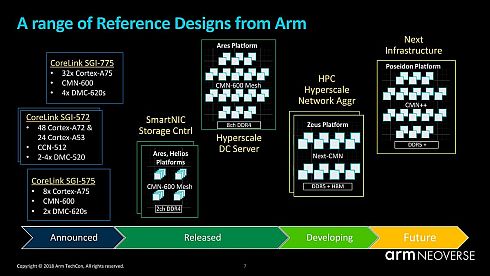

図9は「SGI-575」と「SGI-775」の構成をまとめたものだが、ご覧の通り4コアを1つのクラスタとし、これとシステムキャッシュ、メッシュネットワーク、周辺ロジックなどをひと塊にしたものである。ちなみに、SGIそのものはIPパッケージというよりも、名前の通り「Guidance」であって、個々のCPUなどに関してはPOPが提供されるが、図9の形で複数のCPU IPコアやキャッシュ、周辺回路をまとめたものはPOP(Processor Optimization Package)としては提供されない模様だ。

先述したGraviton Processorの場合はCortex-A72を利用しているとされており、SGI-572(Cortex-A72を最大48コア、もしくはCortex-A24を最大24コア集積するもの。インターコネクトはCCN-512を利用する)をベースとした製品となっている模様だ。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- イチから全部作ってみよう(31)SQLを操作して実際にデータベースを作ってみる

- 産総研のフィジカルAIプロジェクトに迫る 10万年ギャップを超えろ!

- フィジカルAI開発支援に向け「Omniverse」や「Isaac Sim」のPoC環境を無償提供

- オープンソースの「Godot」をベースに強化した産業用リアルタイム3Dエンジン

- アミューズメント機器のコイン投入量や景品出庫数をリアルタイム可視化

- 24時間連続稼働を想定したファンレスの組み込み用コントローラーを発売

- 「GoogleTest」の活用を支援するC/C++言語対応テストツール

- Arm初のCPUチップ「AGI CPU」が顧客とパートナーにもたらす悲喜こもごも

- SUSEのエッジ戦略が完成形へ、「タイニーエッジ」をカバーするLosantを買収

コーナーリンク