富士ソフト、FPGA実装のステレオビジョンIPやストレージIPを紹介:ET2014

富士ソフトは「Embedded Technology 2014/組込み総合技術展(ET2014)」にて、Cyclone V SoCを使ったステレオビジョンIPや、米IntellipropのIPをFPGAに実装するストレージ関連製品などを展示した。「組み込み機器」と「IP」のマッチングサイト紹介も。

富士ソフトは2014年11月19〜21日までの3日間、パシフィコ横浜で開催されている「Embedded Technology 2014/組込み総合技術展(ET2014)」に出展し、Cyclone V SoCを使ったステレオビジョンIPや、米IntellipropのIPコアをFPGAに実装するストレージ関連製品などを展示した。

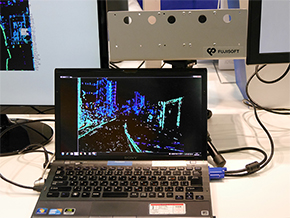

ステレオビジョンIPは2つのカメラで捉えたステレオ映像をアルテラのCyclone V SoCで補正・校正、およびステレオマッチングを行い、さらに東京工業大学 准教授 実吉敬二氏が開発したアルゴリズムで物体検知と動体追尾を行うもので、システムに合わせたカスタマイズやサービスの提供は富士ソフトが手掛ける。2014年内には販売を開始する予定で、カメラユニットを含めたボードの価格は50万円前後となる見込みだという。

カメラユニットにはTerasic製の500万画素CMOSセンサーを搭載しており、出荷時には補正校正ともに済ませた状態で出荷される。基線長(左右カメラ間の距離)は複数パターンが用意される。ソフトウェアとしてはデモアプリ、IPコア制御用サンプルコア(いずれもソースコード提供)、カメラ用画像ビューワー(Windows 7 バイナリ提供)などが付属する。

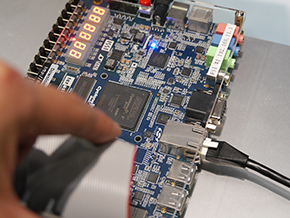

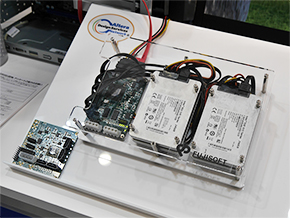

米IntellipropのIPをFPGAに実装するストレージ関連製品としては、SATA Revision 3.0(1.5Gbps/3.0Gbps/6Gbps対応)に準拠したIPが注目だ。既に販売開始より1年程経過しているが、ホスト/デバイスいずれにも利用可能であり、対応FPGAもアルテラ「Arria II GX」「Cyclone V SX SoC」やザイリンクス「Zynq-7000」「Kintex-7000」など幅広く、ザイリンクスの「UltraScale」にも対応する予定となっている。

同様のストレージ関連製品としては、SAS 2.1対応IPコアも展示されていた。こちらは米IntellipropのSAS Revision 2.1標準規格準拠(3.0Gpbs/6.0Gbps対応)のイニシエータ/ターゲットIPコアで、サーバやワークステーションのインターコネクト、HDDやSDDのホットスワップなどに利用できる。

この他にもAndroidの描画処理でボトルネックになる部分をFPGAブロックでハードウェア化したグラフィックアクセラレータや、製造中止になったCPUをFPGAで再現するレガシーCPU IPコア、FPGAによるH.265のリアルタイムデコード(デモで使用されていたFPGAはStratix V)などが展示されていた。

また、ブースの1角を占めていたのは、同社の運営する組み込みシステムとIPのマッチングサイト「EIPC」の紹介コーナー。EIPCはFPGAやOS、ドライバ、ミドルウェア、プロセッサなどの製品情報を持つベンダーが情報を登録しており、製品を製造するメーカーが製造する製品にマッチしたIPを検索できるサービス。検索できるだけではなく、IPベンダーへの問い合わせも可能となっている。

関連記事

ET2014:組み込み技術の祭典「ET2014」開幕、今年のテーマは「IoT」

ET2014:組み込み技術の祭典「ET2014」開幕、今年のテーマは「IoT」

国内最大規模の組み込み技術総合展示会「組込み総合技術展 Embedded Technology 2014(ET2014)」が開幕した。IoT(Internet of Things)をテーマに、360以上の団体が出展、130を超えるセミナーも実施される。 ET2014 開催直前情報:原子時計M2M基板やCANへのなりすまし防御など、「ETアワード」受賞社が決定

ET2014 開催直前情報:原子時計M2M基板やCANへのなりすまし防御など、「ETアワード」受賞社が決定

組込みシステム技術協会(JASA)はパシフィコ横浜で開催される「Embedded Technology 2014」に出展、展示される製品や技術などの中から、業界の発展や国内産業競争力の向上に寄与するものを表彰する「ETアワード」の受賞社を発表した。 Embedded Technology 2014:IoTで変わる組み込み技術を肌で感じる3日間、ET 2014開催概要

Embedded Technology 2014:IoTで変わる組み込み技術を肌で感じる3日間、ET 2014開催概要

国内最大級の組み込み関連イベント「組込み総合技術展/Embedded Technology 2014」の開催概要が発表された。IoT時代に求められる組み込み技術とその実現手法について、最新の情報が世界に向けて発信される。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

コーナーリンク