オリジナルCPU「DL166」のレジスタをLEDドットマトリックスで見える化する:オリジナルCPUでバイナリコード入門(6)(3/3 ページ)

サンプルプログラムと動作確認

リスト4はサンプルプログラムです。Tang Nano起動時に実行されます。

16: initial begin 17: ram[0] <=8'b1010_0010; // mvi r0,2 18: ram[1] <=8'b00_001_000; // mov r1,r0 19: ram[2] <=8'b1010_0011; // mvi r0,3 20: ram[3] <=8'b00_010_000; // mov r2,r0 21: ram[4] <=8'b1010_0100; // mvi r0,4 22: ram[5] <=8'b00_011_000; // mov r3,r0 23: ram[6] <=8'b1010_0101; // mvi r0,5 24: ram[7] <=8'b00_100_000; // mov r4,r0 25: ram[8] <=8'b1010_0001; // mvi r0,1 26: ram[9] <=8'b01100_110; // inc R6 27: ram[10] <=8'b1001_1001; // jmp 9 28: end

16〜28行目はinitialブロックです。Tang Nanoに搭載されているFPGAの起動時に1回だけ実行されるブロックです。17〜27行目がメモリに格納される命令セットです。18〜25行は何かというと、LEDドットマトリックス上の意図した位置に、意図したレジスタが表示されていることを確かめるプログラムです。その後、26行目からはR6のインクリメントを繰り返して、R6がオーバーフローするとc_flagが立つのかを確かめています。

LEDドットマトリックスの見方

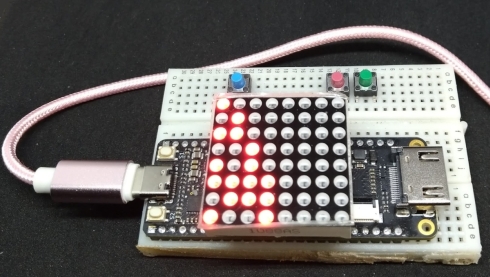

図2は、リスト4のサンプルプログラムをしばらく実行した後のLEDドットマトリクスの様子を示したものです。

図2の左上から最初の1行目の4ドットでr0の値を表示しています。左端のドットが最下位ビットで、左から4ビット目が最上位ビットを表しています。というように、2行目がr1という具合にそれぞれのレジスタの値をドットの点灯で表しています。一番下の左端から4ビットはr7の値を表示しており、これはプログラムカウンターとして使われていますので、現在実行中のアドレスが表示されています。r5は4ビット入力の値が格納されているはずなのですが、今回は未接続なので4ビットとも1になっています。ブレッドボードの上にタクトスイッチが3つ並んでいますが、どことも未接続なので今回は無視してください。

物理制約条件ファイル

リスト5は物理制約条件ファイル(register.cst)です。モジュールの入出力で定義されたシンボルはここで実際のTang Nano搭載のFPGAのピンと関連付けられます。

IO_LOC "clk" 52; IO_LOC "rst" 4; IO_PORT "rst" PULL_MODE=UP; IO_LOC "col[0]" 74; IO_LOC "col[1]" 34; IO_LOC "col[2]" 40; IO_LOC "col[3]" 71; IO_LOC "col[4]" 41; IO_LOC "col[5]" 72; IO_LOC "col[6]" 76; IO_LOC "col[7]" 77; IO_LOC "row[0]" 70; IO_LOC "row[1]" 75; IO_LOC "row[2]" 51; IO_LOC "row[3]" 73; IO_LOC "row[4]" 30; IO_LOC "row[5]" 42; IO_LOC "row[6]" 33; IO_LOC "row[7]" 35; IO_LOC "leds[0]" 10; IO_LOC "leds[1]" 11; IO_LOC "leds[2]" 13; IO_LOC "leds[3]" 14; IO_LOC "leds[4]" 15; IO_LOC "leds[5]" 16;

おわりに

今回は、連載第4回記事でTang NanoにマウントしたLEDドットマトリクスに、DL166のレジスタを表示させてみました。CPU実行時に刻々と変わっていくレジスタの様子を見ることができます。プログラムのデバッグやCPUの動作を学ぶにはなくてはならない機能の一つですね。

実用的にはそういうことなのですが、刻々と変化するドットマトリクスをながめているとなんだか癒されませんか。もしそう感じるようでしたら、あなたも“バイナリアン”の素質大です。

関連記事

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

- ≫連載「Black Hatでハードウェアハック!」バックナンバー

「Tang Nano」にインテル系IDEで開発したオリジナルCPUのソースコードを移植する

「Tang Nano」にインテル系IDEで開発したオリジナルCPUのソースコードを移植する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第5回は、新たな教材「Tang Nano 9K」に、インテル系IDEで開発したオリジナルCPU「DL166」のソースコードを移植する。 新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第4回は、バイナリコーディングを学ぶための新たな教材となる「Tang Nano 9K」とVerilog-HDLコードを使ってLEDマトリクスを制御する。 【バイナリコーディング演習】FPGAボードでLチカとPWMによるLED点灯を試す

【バイナリコーディング演習】FPGAボードでLチカとPWMによるLED点灯を試す

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第3回は、オリジナル4ビットCPUを用いたバイナリコーディングの前段階の演習として、入手が容易なFPGAボードを使ってVerilog-HDLで簡単な回路プログラムを組んでみる。 HDLソースコードからオリジナルCPU「DL166」の内部動作を理解する

HDLソースコードからオリジナルCPU「DL166」の内部動作を理解する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第2回はオリジナルCPU「DL166」のHDLソースコードを基に内部動作について解説する。 オリジナル4ビットCPU「DL166」はプログラミングの基礎学習に最適

オリジナル4ビットCPU「DL166」はプログラミングの基礎学習に最適

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第1回はオリジナルCPU「DL166」のインストラクションセットについて解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

コーナーリンク