【バイナリコーディング演習】FPGAボードでLチカとPWMによるLED点灯を試す:オリジナルCPUでバイナリコード入門(3)(1/3 ページ)

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第3回は、オリジナル4ビットCPUを用いたバイナリコーディングの前段階の演習として、入手が容易なFPGAボードを使ってVerilog-HDLで簡単な回路プログラムを組んでみる。

はじめに

第1回で書きましたが、連載の中盤でArduino上にオリジナルCPU「DL166」のエミュレータを移植し、その上でバイナリコーディングの演習を始めようと思っていました。今回はその前段階として、入手が容易なFPGA開発ボードとVerilog-HDLで簡単な回路プログラムを組んでみたいと思います。

⇒連載「オリジナルCPUでバイナリコード入門」バックナンバー

Tang Nano の購入

「Tang Nano」はSipeedが発売しているFPGA開発ボードです。筆者のTang Nanoは、以下のワードで検索できる海外の通販サイトから購入しましたが、実際に搭載されているFPGAチップが異なる場合があります。

検索ワード:Sipeed Lichee Tang Nano minimalist line FPGA development board breadboard GW1N-1 chip

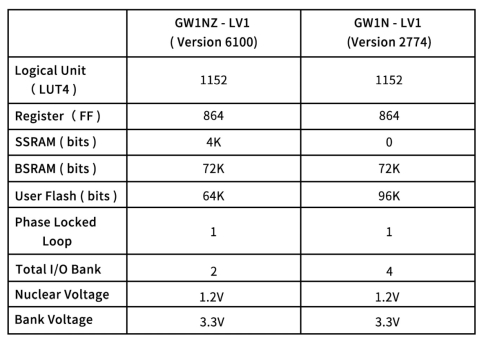

表1はTang Nanoとして市場で出回っているFPGA開発ボードに搭載されている2種類のチップの比較です。「GW1NZ-LV」と「GW1N-LV」があります。

本記事はGW1NZ-LVが搭載されているTang Nanoを用いて記事を書いています。

まずはBlink(Lチカ)から

BlinkはいわゆるLチカですね。LEDを点滅させる回路をTang Nanoに実装してみましょう。

Tang Nanoの取り扱いについては、Sipeedの公式Webサイトから開発ツールをダウンロードしてインストールするとドキュメントが同梱されていますのでそれを参照してください。英語と中国語に加えて日本語のドキュメントがあります。開発ツールにドキュメントが同梱されているので、開発ツール/ドキュメント間でのバージョンなどの食い違いがないことはうれしいですね。

それでは、Verilog-HDLで書いたBlinkのソースコードを見ていきましょう(リスト1)。

1: module blink ( input clk, input rst,output led, output gnd); 2: reg [23:0] counter; 3: assign led=counter[23]; 4: assign gnd=0; 5: always @(posedge clk or negedge rst) begin 6: if (!rst) 7: counter <= 24'd0; 8: else counter <= counter + 1; 9: end 10: endmodule

1行目でモジュール名の宣言と入出力の定義を行っています。Verilog-HDLではひとまとまりの機能単位の回路をモジュールと言います。C言語のモジュールをイメージしてもらって差し支えありません。入力はclkとrstの2つ、出力はledとgndの2つです。今回このモジュールが1つで最上位なので、これらの入出力がICチップのピンのように外部と信号のやりとりをします。

それでは1つずつ入出力信号を見ていきましょう。まず入力からです。clkはこのモジュールに外部からのクロックを取り込むために用意しています。次のrstは外部からリセット信号を受け取ります。今度は出力です。ledは外部に接続される発光ダイオードを駆動するための信号を出力します。gndは常にグランドです。これらの信号は、LEDがTang Nanoの隣り合うピンに接続できるようにLEDのカソード側のグランドを用意しています。

2行目では24ビット長のレジスタを用意しています。レジスタはC言語であれば24ビット長の変数のようなものです。このcounterでclk信号を“1/(2^24)”に分周します。Verilog-HDLはC言語に影響を受けたハードウェア記述言語です。C言語でのプログラミング経験があればコードを見ておおよそ何をしているのかが察しが付くのではないでしょうか。

3行目はcounterの最上位ビットを出力信号のledに接続します。つまり、counterの最上位ビットがledの出力ピンを通して外部に伝えられます。

4行目は出力ピンとしていたgndピンの電位を0に落とします。

5行目はclkの立ち上がりまたはrstの立ち下がりで6〜8行目までが実行されます。

6行目と7行目は一緒に説明します。rstが0あるいはrstピンがグランドに落ちていればcounterの値を0にします。8行目は、6行目の条件がかなわない場合、すなわちrstが0でなければcounterの値を加算します。

IO_LOC "clk" 47; IO_LOC "rst" 44; IO_LOC "led" 16; IO_LOC "gnd" 17;

リスト2はcstファイルの内容です。このファイルは最上位モジュールで宣言した入出力信号を実際のTang Nanoのピンアウトに関係付けるものです。一番上の行であればclkを47番ピンに関連付けています。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク