【バイナリコーディング演習】FPGAボードでLチカとPWMによるLED点灯を試す:オリジナルCPUでバイナリコード入門(3)(3/3 ページ)

Verilog-HDLで書いたPWMのソースコード

リスト5はBlinkと同様に、Verilog-HDLで書いたPWMのソースコードです。これも上から順に説明していきましょう。

1: module pwm2 ( input clk, input rst,output [5:0] led ); 2: reg [23:0] counter; 3: assign led[0] = counter[15]; 4: assign led[1] = (counter[14:10] == 0); 5: assign led[2] = (counter[9:0] == 0); 6: assign led[5:3] = 0; 7: always @(posedge clk or negedge rst) begin 8: if (!rst) 9: counter <= 24'd0; 10: else counter <= counter + 1; 11: end 12: endmodule

1行目はこのモジュールの名前と入出力ピンを定義しています。モジュール名はpwm2です。clkは入力信号、rstも入力信号です。ここまでは前述のBlinkと名前も役割も同じですね。今度は出力ですが“[5:0] led”はバス表記で6本の信号線を1つの名前でまとめています。結局のところ入力信号は2本で出力6本ということになります。

2行目でBlink同様24ビット長のcounterというレジスタを用意しています。

3行目でcounterの15ビット目を外部信号のled[0]に接続しています。

4行目ではcounterの10〜14ビット目までが全て0であるかどうかの値がled[1]の値となります。すなわちそれらのビットが全て0の時だけled[1]の値は1となります。

5行目はcounterの0〜9ビット目まで全て0の時led[2]の値は1となります。

6行目ではled[5:3]の3本の出力信号を全て0にします。すなわちこれらの信号線は0V電位を出力します。これはLEDのカソードを接続するために用意しました。これもTang Nanoの任意のピンにLEDを刺せるようにした配慮です。LED1本当たり2本の信号を割り当てるわけですから、リソースの無駄使いと思われるかもしれませんが、Tang Nanoに接続するデバイスが少ない場合は、ブレッドボードなどにジャンパー線を使わなくてすむので筆者は結構気に入ってこの方法を使ってます。

7行目より後のコードは前述のBlinkと同じですので説明はそちらを参照してださい。

なぜこのコードがPWM動作になるのか

デューティ比と0になるビット数の関係は以下のようになります。

デューティ比=1/(2^(0になるビット数))

この場合それぞれのビットは、隣り合っていても、離れていてもOKです。また他のPWM生成回路とビットが重なっていても問題ありません。3行目の場合は1ビットのみですから“1/(2^1)”なのでデューティ比1/2となります。

4行目の場合は10〜14ビット目なので5ビットとなります。デューティ比は“1/(2^5)”なので1/32となります。5行目は0〜9ビット目までですので10ビットとなります。よって求めるデューティ比は“1/(1/2^10)”となり1/1024となります。

リスト6は入出力ピンと実際のTang Nanoのピンを関連付けるcstファイルの中身です。Tang Nanoのピンの位置は先に示した図2の「Tang Nanoのピン配列」を参照してください。

IO_LOC "clk" 47; IO_LOC "rst" 44; IO_LOC "led[0]" 16; IO_LOC "led[3]" 17; IO_LOC "led[1]" 18; IO_LOC "led[4]" 23; IO_LOC "led[2]" 19; IO_LOC "led[5]" 29;

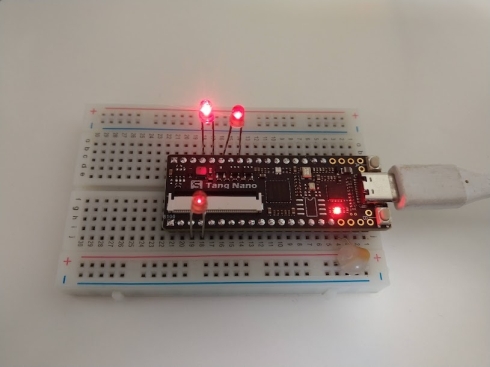

図3はpwm2をTang Nanoで実行したものです。図2で示したTang Nanoのピン配列と照らし合わせて見れば、各LEDのデューティ比を確認していただけると思います。

おわりに

今回は、Verilog-HDLを用いてCPUを移植する前の腕慣らしとして、Tang Nanoで簡単な回路プログラムを組んでみました。FPGAに実装した回路が、実際に現実の物理世界とつながるという実感を持っていただけたでしょうか。

プログラミング経験なくVerilog-HDLで回路を書いている時は、恐らく「何かのプログラミング言語で何かのコードを書いてる」という意識しかなかったと思います。しかしいったんIDEで配置と配線を行えば、コードの中の入出力で用いられたシンボルがTang Nanoのピン名に関連付けられます。これはまさに、FPGAで作成した半導体チップの中の回路と外の世界がつながる瞬間なのです。FPGAはこのような驚きをたくさん秘めた半導体デバイスです。今後もさまざまな形で、みなさんと一緒にFPGAの魅力を探していければと思います。

関連記事

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

- ≫連載「Black Hatでハードウェアハック!」バックナンバー

HDLソースコードからオリジナルCPU「DL166」の内部動作を理解する

HDLソースコードからオリジナルCPU「DL166」の内部動作を理解する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第2回はオリジナルCPU「DL166」のHDLソースコードを基に内部動作について解説する。 オリジナル4ビットCPU「DL166」はプログラミングの基礎学習に最適

オリジナル4ビットCPU「DL166」はプログラミングの基礎学習に最適

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第1回はオリジナルCPU「DL166」のインストラクションセットについて解説する。 マブチモーターをArduinoで制御する

マブチモーターをArduinoで制御する

「マブチモーター」でもおなじみ「直流ブラシ付きモーター」は安価で入手性もよいモーターです。これをArduinoで制御するとしたら、何を理解して何を用意して、どんなプログラミンが必要でしょうか。実験します。 初歩から学ぶ、マイコン開発とARMプロセッサー

初歩から学ぶ、マイコン開発とARMプロセッサー

組み込みの世界では最も成功したプロセッサの1つ「ARM」を用いたマイコン開発にチャレンジします。クラウド開発環境「mbed」を使い、プログラムを書きながら回路をブレッドボードに実装、動作を確認しながらさまざまな内蔵デバイスの使い方をマスターしていきます。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク