Intel、10nmプロセス世代FPGA「Agilex」を発表――アーキも一新:組み込み開発ニュース(2/2 ページ)

「完全なシステムソリューションを持つ」Intelの強みを生かす

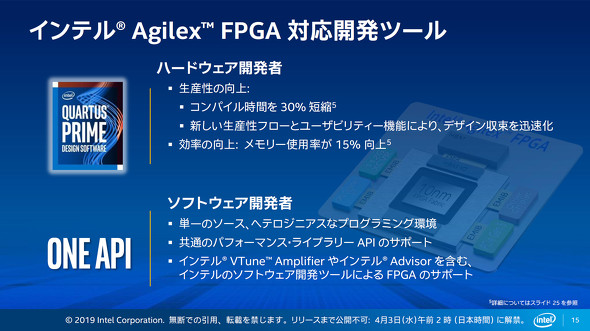

開発者に対するサポートも推進する。ハードウェア開発者向けに設計から論理合成、シミュレーション機能までを提供する「Quartus Prime 開発ソフトウェア」ではコンパイル時間を30%短縮するなど生産性を向上させた。

ソフトウェア開発者向けには、Intel製CPUやFPGA、専用アクセラレーターを共通コードで扱うことができるコンピュータビジョン開発用のツールキット「OpenVINO」や、さまざまなISA(命令セットアーキテクチャ)が混在するヘテロジニアスなプロセッサ環境においても単一のAPIでコードが記述できる「OneAPI」でAgilexを利用することができる。

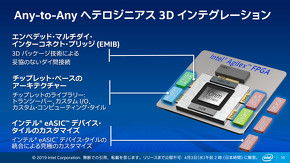

AgilexはSiP(System in Package)で構成しており、FPGAファブリックとチップレットはEMIB(Embedded Multi-die Interconnect Bridge)によって基板にパッケージングされる。これによりAgilexでは“Any-to-Any”に製品ラインアップを構成できるため、顧客は自らのニーズに合ったFPGAを豊富なSKU(Stock Keeping Unit)の中から選択できる。SKUは「数百というオーダーになる」(Dorsey氏)見通しだ。

また、FPGAをカスタムロジック開発に用いる場合にもAgilexは有効なソリューションであるという。Intelは2018年7月にストラクチャードASICを手掛ける「eASIC」の買収を発表しており、同社は製品ライフサイクルの段階に応じてカスタムロジックの実装をFPGAからストラクチャードASIC、そしてASICへシームレスに移行することを支援できる体制が整ったとする。Dorsey氏は「ストラクチャードASICによってASIC開発期間が従来より半減できる。カスタムロジックを一気通貫で提供する能力を持つのはインテルだけだ」と強調した。

Agilexは「Fシリーズ」「Iシリーズ」「Mシリーズ」の3ラインアップでファミリーを構成する。Fシリーズはローエンドとして位置付けられ、基本的なスペックとしては最大58Gbpsのトランシーバ、PCIe Gen 4のインターコネクト、DDR4 SDRAMのメモリに対応する。

ミッドレンジのIシリーズでは最大112Gbpsのトランシーバ、PCIe Gen 5のインターコネクト、DDR4 SDRAMのメモリ、Arm Cortex-A53のクアッドコアSoC(System on Chip)を実装し、オプションでCXLによるXeon Scalable Prosessorとの接続に対応する。

ハイエンドとなるMシリーズでは最大112Gbpsのトランシーバ、PCIe Gen 5のインターコネクト、DDR4/DDR5 SDRAMやOptane DC Persistent Memoryのサポート、Arm Cortex-A53のクアッドコアSoC(System on Chip)を実装し、オプションでCXLによるXeon Scalable Prosessorとの接続、HBMに対応するとしている。

関連記事

AIに“全方位”で挑むインテル、GPUや専用プロセッサとどう戦うか

AIに“全方位”で挑むインテル、GPUや専用プロセッサとどう戦うか

インテルは2018年12月17日、東京都内で記者説明会を開催し、2018年における同社の活動の振り返りと2019年以降の展望について説明した。本稿では、説明会で示された内容の中でAI(人工知能)やB2Bコンピューティングに関するトピックを中心に紹介する。 インテルがデータセンター向けFPGAカードの第2弾「従来比4〜5倍の性能を発揮」

インテルがデータセンター向けFPGAカードの第2弾「従来比4〜5倍の性能を発揮」

インテルは、ソフトウェア開発者でもFPGAを容易に扱える環境を用意した「インテル プログラマブル・アクセラレーション・カード(PACカード)」の第2弾として、ハイエンドFPGAである「Stratix 10 SX」を搭載する品種を追加したと発表した。提供時期は2019年前半を予定している。 インテルが画像認識ソフト開発ツールを無償提供「IoTの“I”は“Eye”」

インテルが画像認識ソフト開発ツールを無償提供「IoTの“I”は“Eye”」

インテルは2018年6月28日、東京都内で「インテル インダストリアル IoT ソリューション DAY」を開催。「IoTの“I”は“Eye(目)”ではないかと思うほどに、画像認識技術がより重要になっている」(同社)とし、画像認識ソフトウェアの開発ツール「OpenVINOツールキット」を無償で提供するなどしている。 なぜインテルはコンピュータビジョンに注力するのか、エッジへの分散処理が鍵に

なぜインテルはコンピュータビジョンに注力するのか、エッジへの分散処理が鍵に

インテルがAI技術の1つとして注目されている「コンピュータビジョン」への取り組みについて説明。2018年5月に発表した無償のコンピュータビジョン開発ソフトウェア「OpenVINOツールキット」は日本市場でも浸透しつつあるという。 低コストFPGAで深層学習、コア技術をオープンソース化したベンチャーの狙い

低コストFPGAで深層学習、コア技術をオープンソース化したベンチャーの狙い

LeapMindは2018年10月19日、組み込み向けFPGA上でディープラーニングを動作させるソフトウェアスタックをオープンソースで公開した。同社が今まで強みとしてきた技術が、誰でも利用もできるようになった。同社CTO(最高技術責任者)を務める徳永拓之氏に、blueoilとはどのようなもので、何が実現できるのか。そして、オープンソース化した狙いなどを聞いた。 エッジAIは専用プロセッサの流れに、LeapMindが独自IPの設計を明かす

エッジAIは専用プロセッサの流れに、LeapMindが独自IPの設計を明かす

LeapMindはディープラーニングの推論処理に特化した低消費電力プロセッサIP(Intellectual Property)の開発を明らかにした。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク