ARMの最新アーキテクチャ「ARMv8-M」が目指す「セキュアMCU」とは:ARMv8-Mアーキテクチャ解説(2/3 ページ)

MCUはなぜ脆弱性の塊なのか

なぜこんな形で長らく使われてきたかといえば、これまでMCUはスタンドアロンで動作しており、物理的に侵入を防げていたからだ。一度機器に組み込んでしまえば、その機器ごと盗まれない限りは侵入される危険性は無いし、MCUの中に機密情報を格納するようなケースも普通は考えられなかった(そうした処理は、MCUとつながるホストプロセッサの側の領分と考えられた)から、盗まれたことによる副次的な被害は考えにくかった。

ところがIoT(モノのインターネット)などの普及により、MCUも今ではコネクテッド(Connected)になってきており、いろいろな形で通信を行うようになってきた。さらには、ファームウェアを出荷後にOTA(Over-the-Air)でアップデート、なんてケースも既に珍しくなくなりつつある。加えて言えば、通信を行うということは、通信相手と接続する際の情報をMCU内に格納する必要があるという意味でもある。

この結果として、ホストあるいはクラウドへの侵入の足掛かりとしてMCUに侵入されるとか、通信を傍受することで認証のIDを盗まれるとかなどの問題や、あるいはMCUを誤動作させることでシステムをまひさせる(自動車へのクラッキングなどがこの代表例であろう)といった被害が起きることが容易に想像しえるし、実際にそうした問題あるいは実証例が出現しつつある。

こうした問題に対応するために、MCUをセキュアにする必要がある、という話は以前から出てきていた。実際、幾つかのMCUベンダーは自社製品の中にこのあたりを強化した製品をラインアップしている。ただ全ての製品がセキュアというわけではなく、またセキュア化の方法は各社まちまちである。

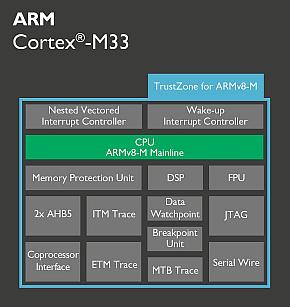

こうしたベンダー任せのセキュア化では、ソフトウェア的な互換性が取れないし、何よりMCUのセキュア化の進みが遅くなってしまう。それもあって、2015年にARMは、標準的なMCUのセキュア化技法として、同社の「TrustZone」技術をMCUに適応したARMv8-Mアーキテクチャを発表。2016年10月に、このARMv8-Mを実装した2つのMCUコアとインターコネクトの「SIE-200」、さらにアクセラレータとなる「CryptoCell-312」を発表した。

「ARMv8-M」が提供する3段構えの防御

ではこのARMv8-Mでは何をカバーできるのか? というのが次の議論である。

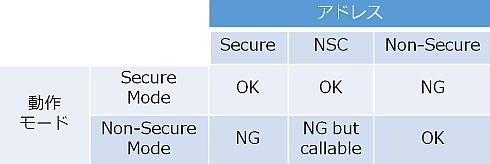

まずARMv8-Mの構造を簡単に説明しておこう。基本的にARMv8-Mは、従来のアーキテクチャ「ARMv7-M」にセキュアモードとノンセキュア(Non-Secure)モードという2種類の動作モードを追加した形だ。基本はアドレスベースで、メモリ(フラッシュ/SRAM/etc……)をそれぞれセキュアとノンセキュアに分離した上で、表1のような制約を付けた。

NSCというのは“Non-Secure-callable”の略である。例えば、通信の暗号処理はセキュアにおいて置きたいが、それを呼び出す元はノンセキュアで記述している、なんて場合にはノンセキュアなモードからセキュアなモードを呼び出す必要がある。この際に関数のエントリポイントとして利用されるのがNSCの領域で、ここを呼び出すとセキュアモードに切り替わる形になる。

後はプログラムの書き方次第ではあるのだが、例えば通信における認証IDとか暗号化キーなどは全てセキュアアドレスに格納するようにして、ノンセキュアではその領域をアクセスしないようにすれば、トロイの木馬に侵入されて不正なコードを実行されたとしても、守るべき情報そのものにはアクセスできないことになる。これが防御の第1段である。

防御の第2段は、そもそも不正なコードを実行できないようにするための仕組みになる。フラッシュの改ざんは別にして、SRAMの改ざんについては、MPUの内部でコードとして実行できる領域とできない領域を指定できるようにしている。ARMはこれをPSMA(Protected Memory SYstem Architecture)と呼んでいるが、このPSMAそのものはARMv7-Mの時代にも存在した。ただ、特に「Cortex-M0/M0+」などでは、MPUそのものがオプション扱いになっていたし、ARMv7-M時代のPSMAはメモリサイズが2の倍数(2KB/4KB/8KB/16KB/……)単位でしか制御できないので、細切れでの管理が非常に面倒だった。

ARMv8-Mに搭載される「PSMA v8」では、このあたりが自由にサイズを指定できるように改良されている。MPUの搭載も必須になったことにより、たとえSRAMの改ざんがあっても、それをコードとして実行されることを防げるようになった。

ちなみにキャッシュに関しては本来オプション(図3、Cortex-M23/33共にCPUのパイプラインにキャッシュは含まれていない)なので、これはハードウェア側で実装する際にCPUから一切見えないようにすることで改ざんの手段を与えずに済ませられる。一方のフラッシュメモリはセキュアメモリ(Secure Memory:内部を暗号化し、正しいキーが無いと読み書きできない)を利用し、さらにセキュアブート(Secure Boot:CPUがブート時に、ロードしようとしているコードが正しいものであることを確認してからロードする手順)を行うことで、オフラインあるいはオンラインでの改ざんを防止することが可能になっている。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

表1 「ARMv8-M」の動作モードとアドレスの対応

表1 「ARMv8-M」の動作モードとアドレスの対応