ARMの最新アーキテクチャ「ARMv8-M」が目指す「セキュアMCU」とは:ARMv8-Mアーキテクチャ解説(1/3 ページ)

ARMの最新のMCU向けアーキテクチャ「ARMv8-M」は、同社が提唱する「セキュアMCU」に向けたものとなっている。本稿では、このセキュアMCUの定義と、その実装について解説する。

ARMは、2015年11月に米国カリフォルニア州サンタクララで開催された「ARM TechCon 2015」において、「Secure MCU(以下、セキュアMCU)」のアーキテクチャである「ARMv8-M」を発表。そして2016年10月の「ARM TechCon 2016」では、このARMv8-Mを実装したプロセッサコア「Cortex-M23」と「Cortex-M33」(以下、Cortex-M23/33)を発表した。

ただ「そもそもセキュアMCUって何?」という疑問を抱かれる人も多いと思う。そこでちょっと原点に帰って、セキュアMCUというものの定義と、その実装をご紹介したいと思う。

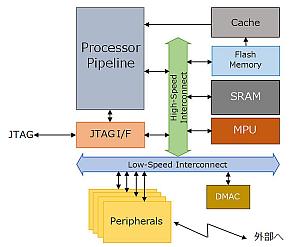

図1は、一般的(?)なMCU(Micro Controller Unit、マイコン)の構成である。「MCUにキャッシュが入るのか?」と突っ込まれる方も居られようが、フラッシュメモリ(Flash Memory)の速度との兼ね合いになるため、一般論として動作周波数100MHz以上で駆動されるMCUの中にはキャッシュを搭載するものがちらちらと出始める。まぁこのあたりは速度との兼ね合いと考えて欲しい。あるいは、ここには入れてないが、スクラッチパッド(ScratchPad)あるいはTCM(Tightly Coupled Memory)といった、高速にアクセス可能なSRAM領域が別に搭載される場合もあるが、扱いとしてはSRAMと同じなので割愛する。

で、8ビットの低速なMCUだとインターコネクト(Interconnect)が1つだったりするが、ある程度高速なMCUだとプロセッサパイプライン(Processor Pipeline)とメモリ周りをつなぐ高速なインターコネクトと、周辺回路をつなぐ低速なインターコネクトが分離され、そこにさまざまな通信モジュールを含む周辺回路が接続される。また一部の周辺回路で高速にデータ転送を行うため、DMAC(DMA Controller)が用意される。

こうした全体の回路のメモリマップは、MPU(Memory Protection Unit)で管理される形だ。またこれとは別に、デバッグを行うためにJTAGインタフェースが搭載され、ICE(In-circuit Emulator)などを接続して、CPUの動作状況やメモリの内容、インターコネクトの状態などにアクセスできるようになっている。

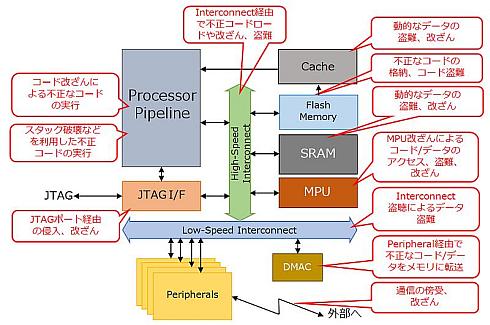

さて、この図1のMCUだが、どんな脆弱性があるのか。それをまとめたのが図2である。ありがちな話では、こっそりとトロイの木馬的なプログラムを動かすことで、プログラムやデータを改ざんしたり、あるいはデータを盗んでどこかに送り出したりといったことが可能になる。そのためにはトロイの木馬をまず仕込む必要があるわけだが、これも山ほど手法はあり、プログラムを格納するフラッシュメモリそのものの改ざんとか、データを格納するSRAMの動的な改ざんなどが主なところだ。

SRAMの改ざんに関してはスタックアンダーフロー(Stack underflow)とかスタックオーバーフロー(Stack overflow)を発生させることで、SRAM中に送り込んだデータをコードとして実行させるが一般的だ。中にはキャッシュ(Cache)を改ざんして、不正コードを実行させるなんて例もある。

スタックアンダーフロー/オーバーフローそのものを発生させる主要因は、もともとのプログラムの不備であることが多い。副次的な要因としては、周辺回路からDMAC経由でメモリを改ざんする(この際に周辺回路の不具合を突くことが多い)手法があり、ついでにMPUの保護エリアも改ざんするといった念の入った手段が利用される。

別の方法としては、JTAGポートからICEなどを使って侵入、という方法も環境によってはかなり有効である。また昨今はMCUが外部と通信を行うのは一般的であるが、この通信の傍受、改ざんも当然可能である。要するに、既存のMCUはある意味脆弱性の塊といって良い。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク