GPUボードの電力損失を垂直電源供給で5分の1に、村田製作所が「iPaS」で実現:CEATEC 2024

村田製作所は、「CEATEC 2024」において、電源回路のコンデンサーやインダクターをパッケージ基板に内蔵することでGPUボードの消費電力を大幅に低減できる部品「iPaS」を披露した。2026年ごろの実用化を目指している。

村田製作所は、「CEATEC 2024」(2024年10月15〜18日、幕張メッセ)において、電源回路のコンデンサーやインダクターをパッケージ基板に内蔵することでGPUボードの消費電力を大幅に低減できる部品「iPaS(アイパス)」を披露した。既にGPUボードやAI(人工知能)アクセラレータのベンダーからの引き合いもあり、2026年ごろの実用化を目指して開発を進めている。

生成AIの需要拡大によってAIデータセンターの建設が急ピッチで進む中で、課題として急浮上しているのがデータセンターの消費電力の増大である。この大きな消費電力の要因となっているのが、AIの学習や推論を行うGPUボードの消費電力である。一説では、GPUボード1枚で消費電力が1000Wに達することもあるという。

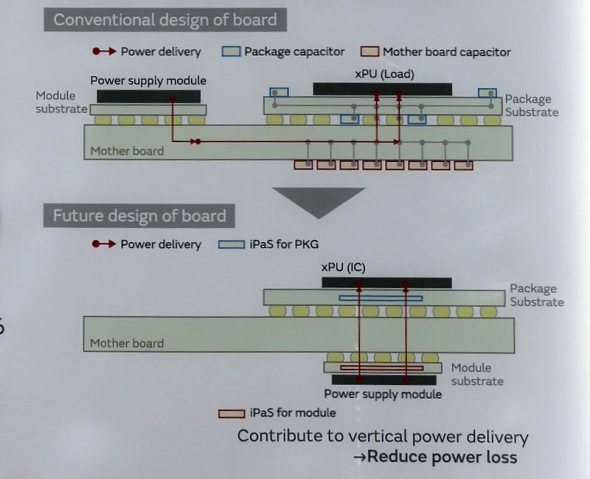

現在、GPUボードの回路構成では、GPUの横に電源モジュールを配置するとともに、GPUの裏面に積層セラミックコンデンサーを高密度に表面実装していることが多い。しかしこの構成は、電源モジュールからGPUまで一定の配線距離を取る必要があり、その分だけ電力損失が発生してしまう。

この配線距離をさらに短くできる新たな回路構成として検討されているのが、積層セラミックコンデンサーを実装しているGPUの裏面に電源モジュールを配置する垂直電源供給である。ただし垂直電源供給では、これまで裏面に高密度実装していた積層セラミックコンデンサーや、電源モジュールと周辺に実装していたインダクターを設置する場所がなくなってしまう。iPaSは、これらのコンデンサーやインダクターを、GPUや電源モジュールのパッケージ基板内に内蔵できるようにした部品である。「現行の消費電力1000WクラスのGPUボードの場合、配線距離に基づく電力ロスが250Wほど発生しているといわれている。垂直電源供給に置き換えると、この電力ロスが約5分の1の50Wにまで抑えられる可能性がある」(村田製作所の説明員)。

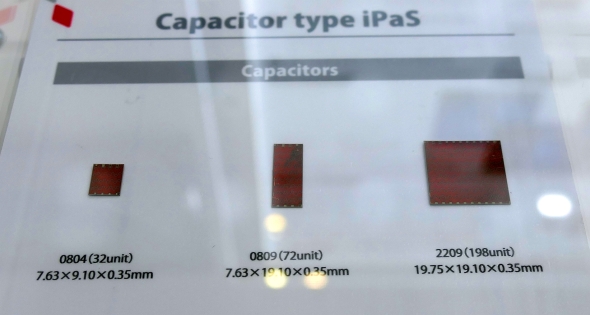

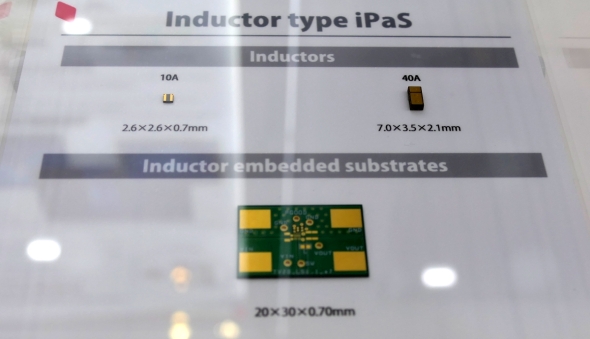

コンデンサータイプのiPaSは、個別のコンデンサーとして利用可能な容量を持つユニットを複数作り込んだ厚さ0.35mmの板状の部品になる。展示した品種は、サイズが横7.63×縦9.10mmの場合で8×4で32ユニット、横7.63×縦19.10mmの場合で8×9で72ユニット、横19.75×縦19.10mmの場合で22×9で198ユニットとなっている。コンデンサーの容量部を貫くスルーホールで電極パッドが結ばれており、先述した垂直電源供給に最適な構造であるとともに、配線のインダクタンス成分も低減できている。また、インダクタータイプのiPaSは、外形寸法が2.6×2.6×0.7mmで直流重畳特性が10A、7.0×3.5×2.1mmで40Aとなっている。

なお、iPaSは「CEATEC AWARD 2024」のイノベーション部門を受賞している。

関連記事

リチウムイオン電池の出力を4倍に、村田製作所がポーラス集電体を開発

リチウムイオン電池の出力を4倍に、村田製作所がポーラス集電体を開発

村田製作所は、米国スタンフォード大学との共同研究により、リチウムイオン二次電池の出力を大幅に増加させることが可能な多孔質の「ポーラス集電体(PCC)」の開発に成功したと発表した。従来の集電体と比べて、最大で4倍の出力を発生させられるという。 村田製作所が「世界最小」の積層セラコンを開発、016008Mサイズ

村田製作所が「世界最小」の積層セラコンを開発、016008Mサイズ

村田製作所は「世界最小」(同社)とする016008Mサイズ(0.16mm×0.08mm)の積層セラミックコンデンサーを開発した。現行の最小品である0201Mサイズ(0.25mm×0.125mm)と比べて体積比で約75%の削減となる。 アンテナ間干渉を省スペースで改善するデバイス「Radisol」を開発

アンテナ間干渉を省スペースで改善するデバイス「Radisol」を開発

村田製作所は、アンテナ間干渉改善デバイス「Radisol」を開発した。独自のセラミック多層技術とRF回路設計技術により開発しており、アンテナに搭載することでアンテナ特性を最大化する。 負の相互インダクタンスを活用してノイズを除去するLキャンセルトランス

負の相互インダクタンスを活用してノイズを除去するLキャンセルトランス

村田製作所は、負の相互インダクタンスを活用したLキャンセルトランス「LXLC21」シリーズを発表した。数M〜1GHzの高調波領域で電源ノイズ対策が可能となり、電子機器の小型化と高機能化に対応する。 LoRaWANと衛星通信に対応した通信モジュールを開発

LoRaWANと衛星通信に対応した通信モジュールを開発

村田製作所は、LoRaWANと衛星通信に対応した通信モジュール「Type 2GT」の量産を開始した。Semtechのチップセット「Connect LR1121」を搭載し、860M〜930MHzおよび2.4GHzのISM Band、最大22dBmの長距離通信と衛星通信が可能だ。 タイヤの摩耗を手軽に3次元で検知、村田製作所と住友ゴムが共同開発

タイヤの摩耗を手軽に3次元で検知、村田製作所と住友ゴムが共同開発

村田製作所はタイヤの摩耗を3次元で可視化するタイヤ摩耗検知システムを住友ゴム工業と共同で開発し、2025年から住友ゴムのダンロップ直営店で実証を開始する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク