FPGAに学習済みニューラルネットワークを実装して推論を実行する:FPGAにニューラルネットワークを実装する(3)(3/3 ページ)

» 2024年03月11日 08時00分 公開

[今岡通博,MONOist]

物理制約ファイル

物理制約ファイル(Physical Constraints File)とは、先に示したVerilogのモジュールの定義で設定した入出力ポートを実際のFPGAのピンに割り当てるファイルです。リスト4のneuro9k.vに対応する物理制約ファイルはリスト7のneuro9k.cstです。そのソースコードは、neuro9k.vと同じリポジトリにあります。

1: IO_LOC "clk" 52; 2: IO_LOC "rst" 4; 3: IO_LOC "btn[0]" 3; 4: IO_LOC "test2" 68; 5: IO_LOC "test1" 69; 6: IO_LOC "low" 81 7: 8: IO_LOC "col[0]" 74; 9: IO_LOC "col[1]" 34; 10: IO_LOC "col[2]" 40; 11: IO_LOC "col[3]" 71; 12: IO_LOC "col[4]" 41; 13: IO_LOC "col[5]" 72; 14: IO_LOC "col[6]" 76; 15: IO_LOC "col[7]" 77; 16: 17: IO_LOC "row[0]" 70; 18: IO_LOC "row[1]" 75; 19: IO_LOC "row[2]" 51; 20: IO_LOC "row[3]" 73; 21: IO_LOC "row[4]" 30; 22: IO_LOC "row[5]" 42; 23: IO_LOC "row[6]" 33; 24: IO_LOC "row[7]" 35;

リスト7 neuro9k.cstのソースコード

1行目の「IO_LOC "clk" 52;」を例にとると、Verilogで定義した"clk"を実装したいFPGAのピン番号“52”に割り当てています。

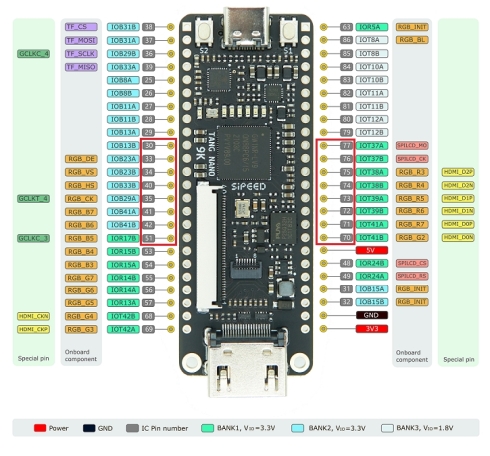

図1はTang Nano 9Kのピン配置を示します。赤枠で囲んだ部分のピンにLEDドットマトリクスが接続されます。また、基板の上側についているUSB-Cコネクターの両脇にある2つの白いボタンの内、右側にあるのがリセットボタン(rst)で、左側にあるボタンがbtn[0]になります。

FPGAに実装したニューラルネットワークで推論を実行する

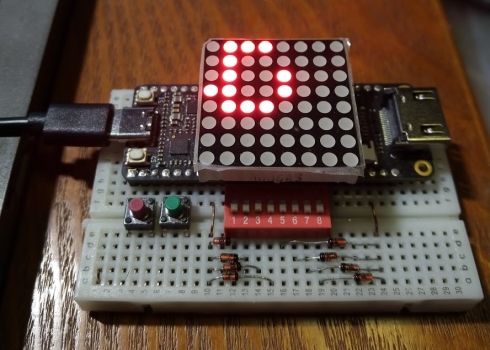

図2は、LEDドットマトリクスに推論させたい手書き文字を表示させたものです。

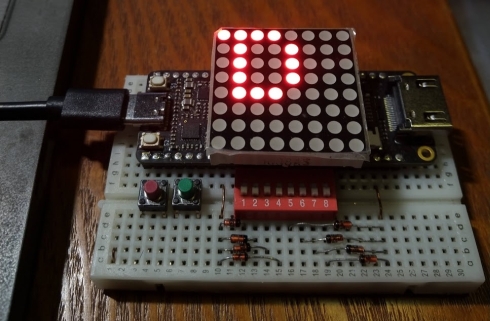

図3は推論した結果です。

FPGA上での推論の流れは本連載の第1回を御覧ください。

おわりに

いかがでしたでしょうか。次回はFPGA上での学習にチャレンジします。お楽しみに。

関連記事

- ≫連載「FPGAにニューラルネットワークを実装する」バックナンバー

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

最も古典的なニューラルネットワーク「ホップフィールドネットワーク」を学ぶ

最も古典的なニューラルネットワーク「ホップフィールドネットワーク」を学ぶ

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第2回では、ニューラルネットワークのモデルの一つである「ホップフィールドネットワーク」を用いて、PC上で文字認識を行えるようにする。 低価格FPGAを用いた文字認識AI推論の全体像

低価格FPGAを用いた文字認識AI推論の全体像

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第1回では、連載の狙いや、文字認識AIモデルの概要、どのようにFPGA上で文字認識を行うかなど全体の流れを紹介する。 新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第4回は、バイナリコーディングを学ぶための新たな教材となる「Tang Nano 9K」とVerilog-HDLコードを使ってLEDマトリクスを制御する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

Special SitePR

コーナーリンク

あなたにおすすめの記事PR