低価格FPGAを用いた文字認識AI推論の全体像:FPGAにニューラルネットワークを実装する(1)(3/3 ページ)

FPGAでの推論

では、PCで作成した学習済みニューラルネットワークをFPGAに実装して推論させてみましょう。

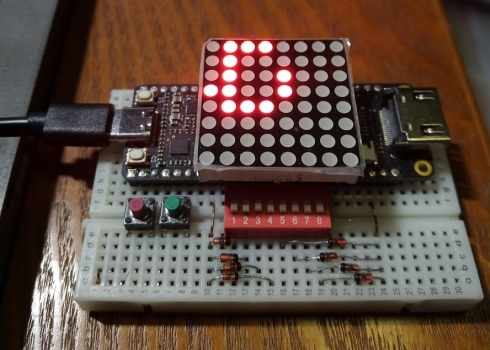

図1は、推論前の手書き文字です。手書き文字とはいっても、FPGAの開発環境を用いてあらかじめ設定しておいたものです。FPGAの電源投入時あるいはPCからのFPGAのプログラミングが完了した時点では、LEDドットマトリクスには何も表示されてないのですが、リセットボタンを押せば図1のようにLEDドットマトリックスに手書き文字が表示されます。これが推論対象の文字になります。

なおリセットボタンは、Tang NanoのボードのUSBポートを左側にしたときに、USBポートの上側にある白いタクトスイッチになります。推論開始は、同じくUSBポートの下側にある白いボタンを押せば開始されます。

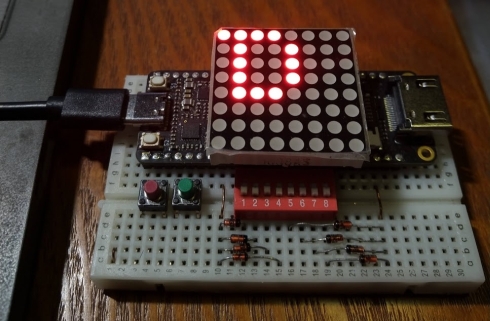

図2は推論結果をLEDドットマトリクスに表示しているところです。先ほど示した手書き文字は推論の結果、学習済みの「D」「J」「C」「M」の中から「D」が最も近かったということが示されました。

もう一度、手書き文字の表示に戻りたいときはリセットボタンを押します。結果は同じですが、もう一度推論させたい場合は先ほどと同様にUSBポートの下側のボタンを押します。

また、他の手書き文字で推論を試したい場合は、PC側のFPGA開発環境で25ビット長のレジスターneurosの値(ビット列)を書き換えて、Tang Nanoをプログラミングし直してください。

オシロスコープで推論時間を計測したところ……

FPGA上での今回のニューラルネットワークによる推論の実行にかかる時間を計測してみましょう。USBポート下側の白いタクトスイッチを押すと推論を開始するので、そのスイッチの状態を観測するためのテストピンと、推論が終了したときに立ち上がるテストピンをTang Nanoのボードのピンから出しています。そのタイミングの差をオシロスコープで計測すれば、推論実行にかかった時間が分かります。

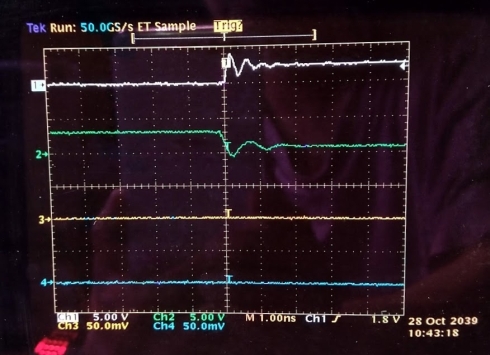

図3はオシロスコープで2つのタイミングの差を観測した写真になります。

図3の上から2番目の緑の横線が推論を開始するためのボタンの状態を示しています。その上の白い横線が推論が終わったことを示す信号線の状態です。

縦軸のひと目盛りは5Vです。また横軸のひと目盛りは100nsです。推論の開始を指示するスイッチの押下は負論理ですので立ち下がった時点で推論が開始します。この時点から上の白い線が立ち上がるまでの時間差が推論にかかった時間ということになります。

図3を見る限りで、この時間分解能では差を見いだすことが難しいくらいになっています。このTang Nanoは27MHzクロック(1クロック当たりの周期は37ns)の発振子を積んでいるので、少なくとも40ns以上の差異は見て取れないので、1クロック以内で推論処理が完了していることを示していると思います。

この波形を見てどう思いますか。このオシロは最近中古で購入したのですが、使い方が完全には分かっておらず右下の測定日時表示が2039年になったりしてはいますが、別段近未来から来た幻想の値というわけでもありません。

波形に話を戻すと、本稿はFPGAの話なのでロジックというかデジタル回路で全て解決できるので、ロジックアナライザでも十分だったのですが、オシロの波形はちょっと生々しいですよね。電位が変位した後にバウンドしたように見えますがこれはプローブと接続先との整合がうまくできてないことによるものと思われます。これから見てもそんなに容易に1と0を区別できないことをお分かりいただければと思いました。

おわりに

いかがでしたでしょうか。本連載の全体の流れをつかんで頂けたでしょうか。次回以降は、PCでのニューラルネットワークの学習や、FPGAへの実装作業など、各パートに分けて詳しく解説していく予定です。次回をお楽しみに。

関連記事

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第4回は、バイナリコーディングを学ぶための新たな教材となる「Tang Nano 9K」とVerilog-HDLコードを使ってLEDマトリクスを制御する。 インテルがFPGA製品を拡充、RISC-Vベースのソフトプロセッサコアも無償提供

インテルがFPGA製品を拡充、RISC-Vベースのソフトプロセッサコアも無償提供

Intelは、Intel Agilex FPGAの製品ポートフォリオを拡充した。開発者がより短期間でソリューションを構築できるよう、クラウドからエッジまでの包括的なソリューションを提供する。 OKIがAIモデル軽量化とFPGA実装を自動化、認識精度を下げず処理速度は5倍に

OKIがAIモデル軽量化とFPGA実装を自動化、認識精度を下げず処理速度は5倍に

OKIとOKIアイディエス、フランスのミプソロジーの3社は、OKI独自のAIモデル軽量化技術「PCAS」とミプソロジーのFPGAによるAI処理の高速化プラットフォーム「Zebra」の連携により、深層学習ベースのAIモデルに内在する不必要な演算を自動的に削減/高速化する技術を開発したと発表した。 ザイリンクスがAIカメラ向けSOM製品「Kria」を発表、スターターキットは199ドル

ザイリンクスがAIカメラ向けSOM製品「Kria」を発表、スターターキットは199ドル

ザイリンクスはAI(人工知能)カメラ向けに同社のプログラマブルSoC「Zynq UltraScale+ MPSoC」やメモリ、周辺部品などを小型ボードに集積したSOM製品「Kria(クリア)」を発売する。第1弾の「Kria K26」などをセットにしたスターターキット「Kria KV260」の価格は199米ドル(約2万1500円)と安価だ。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク