「Tang Nano」にインテル系IDEで開発したオリジナルCPUのソースコードを移植する:オリジナルCPUでバイナリコード入門(5)(2/2 ページ)

メモリ機能

前ページで示したリストは、CPUにおける命令をフェッチしてデコードし実行するコードです。命令をフェッチするのはよいのですが、その命令はどこに格納されているのでしょうか。それはメモリですよね。このメモリ機能はCPU内には含まれませんので別途記述する必要があります。このようにCPUとメモリとは別モジュールとして記述しています。リスト3は、メモリをVerilog-HDLで記述したコードになります。

module ram(clk, we, r_addr, r_data, w_addr, w_data);

input clk, we;

input [7:0] r_addr, w_addr;

input [7:0] w_data;

output [7:0] r_data;

reg [7:0] mem [15:0];

initial begin

mem[0] <= 8'b01100_110;// inc R6

mem[1] <= 8'b1001_0000;// jmp 0

end

always @(posedge clk) begin

if(we) mem[w_addr] <= w_data;

end

assign r_data = mem[r_addr];

endmodule

module行でこのモジュールの名前と入出力を定義しています。このメモリは読み書き可能な機能があるので、weやw_addr、w_dataがありますが、今回は読み出しのみの用途で使っていますので、これらの入出力インタフェースは使っていません。initial beginで囲まれている2行があらかじめこのメモリに書き込まれているコードです(これらについては後述します)。

トップモジュールとその役割

リスト4はトップモジュールであるtestbenchのソースコードです。

module testbench( input clk, input rst, output [3:0]leds);

wire [7:0] w_data;

wire [7:0] r_data;

wire [3:0] adr;

wire [3:0] leds;

wire [3:0] led;

assign leds[0] = !led[0];

assign leds[1] = !led[1];

assign leds[2] = !led[2];

assign leds[3] = !led[3];

reg [23:0] counter;

ram ram1(counter[23], 0, {4'b0000,adr}, r_data, adr, w_data);

cpu cpu1(rst,counter[23],btn,led,adr,r_data);

always @(posedge clk or negedge rst) begin

if (!rst)

counter <= 0;

else counter <= counter + 1;

end

endmodule

このモジュールは3つあるモジュールの中の最上位モジュールです。他の下位のモジュールで定義されている入出力の関連付けを行います。ここではCPUとメモリをつないでいます。

もう1つの役割は、これらのコードを実装するハードウェア環境とのインタフェースを定義しています。この場合ですと、クロック入力、リセットボタン、それと4つのLEDへの接続です。Tang Nanoに搭載されている水晶発振器の周波数は27MHzでこれを基にクロック信号が生成されます。この発信周波数を24分周したものをCPUとメモリに提供しています。

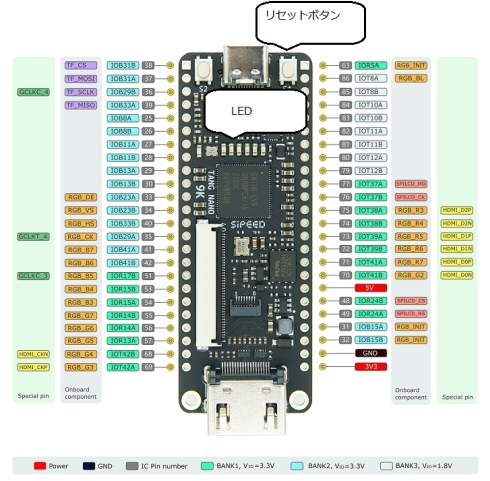

ですからCPUは1秒間に1サイクル前後のクロックで動作します。リセットボタンはUSBコネクター脇の白いタクトスイッチをアサインしています。CPUからの出力である4つのLEDはTang Nanoの基板に搭載されている6つのLEDの内4つを割り当てています。図1は、Tang Nanoのボード上のリセットボタンの位置とLEDの位置を示しています。

物理制約条件ファイル

リスト5は物理制約条件ファイル(Physical Constraints file)の中身を示しています。クロックのピン番号、リセットボタンのピン番号そして4つのLEDのピン番号を指定しています。

IO_LOC "clk" 52; IO_LOC "rst" 4; IO_LOC "leds[0]" 10; IO_LOC "leds[1]" 11; IO_LOC "leds[2]" 13; IO_LOC "leds[3]" 14;

サンプルプログラムと動作確認

リスト6はあらかじめメモリに書き込まれているサンプルプログラムです。CPUが起動するとこのプログラムが動作します。

mem[0] <= 8'b01100_110;// inc R6 mem[1] <= 8'b1001_0000;// jmp 0

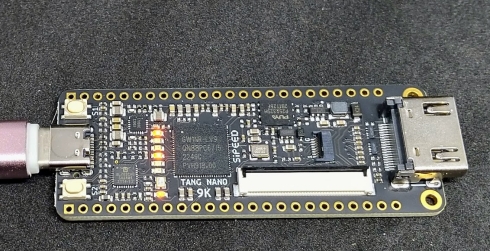

このサンプルプログラムはメモリモジュール(ram.v)のinitial blockに定義されています。メモリの0番地にinc R6、メモリの1番地にjmp 0が書き込まれています。このプログラムが動作するとr6が0から15まで1つずつ加算されます。R6は4つのLEDに直結されるレジスタですので、クロックを刻むごとに加算された値がTang Nanoの基板上のLEDに反映されます。図2はこのサンプルプログラムが動作しているところです。R6の値を示すオレンジのLEDの幾つかが点灯しているのが分かります。

おわりに

今回はインテル系のFPGAのIDEでコーディングしたVerilog-HDLのソースコードをGOWINのIDEで開発できるよう移植作業を行いました。短いコードですがTang NanoでDL166が動作することが確認できました。本稿では言及していませんが、Tang Nano用に手を加えたソースコードはインテルのIDEに同梱されているModelSimでも動作を確認しています。

そろそろTang Nanoでバイナリコーディングの演習を行いたいところですが、そのためにはもう少し機能を追加せねばなりません。あと少しお付き合いいただければと思います。

関連記事

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

- ≫連載「Black Hatでハードウェアハック!」バックナンバー

- 新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

【バイナリコーディング演習】FPGAボードでLチカとPWMによるLED点灯を試す

【バイナリコーディング演習】FPGAボードでLチカとPWMによるLED点灯を試す

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第3回は、オリジナル4ビットCPUを用いたバイナリコーディングの前段階の演習として、入手が容易なFPGAボードを使ってVerilog-HDLで簡単な回路プログラムを組んでみる。 HDLソースコードからオリジナルCPU「DL166」の内部動作を理解する

HDLソースコードからオリジナルCPU「DL166」の内部動作を理解する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第2回はオリジナルCPU「DL166」のHDLソースコードを基に内部動作について解説する。 オリジナル4ビットCPU「DL166」はプログラミングの基礎学習に最適

オリジナル4ビットCPU「DL166」はプログラミングの基礎学習に最適

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第1回はオリジナルCPU「DL166」のインストラクションセットについて解説する。 マブチモーターをArduinoで制御する

マブチモーターをArduinoで制御する

「マブチモーター」でもおなじみ「直流ブラシ付きモーター」は安価で入手性もよいモーターです。これをArduinoで制御するとしたら、何を理解して何を用意して、どんなプログラミンが必要でしょうか。実験します。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

- 国産の高解像度宇宙X線望遠鏡の開発に成功

- 大容量X線画像データを8600分の1に即時圧縮するFPGAデータ処理基板を共同開発

- 声やスマホでの操作も不要、次世代スマートホームは「ビルトイン型」へ

- ドライブレコーダーの録画時間を最大10倍に延長する動画ソリューション

- 長期供給SoCを活用したMCU向け組み込みGUI開発ソリューションの提供を開始

- 産総研のフィジカルAIプロジェクトに迫る 10万年ギャップを超えろ!

コーナーリンク