“プロセッサ”を開発する東芝メモリ、その技術と狙い:組み込み開発 インタビュー(1/3 ページ)

東芝メモリがプロセッサの開発を発表した。現業から離れているように見えるプロセッサの開発を通じて東芝メモリは何を目指すのか。今回発表された技術の概要と開発の狙いを聞いた。

東芝メモリがプロセッサの開発を発表した――。同社の事業を知る人にとって思わず二度見してしまうような発表が2018年11月6日にあった。

同社はNAND型フラッシュメモリ市場で高い市場シェアを誇る。主力製品は積層プロセスを用いた3D NANDフラッシュメモリ「BiCS FLASH」に代表されるメモリチップ。その他にも、メモリチップを応用した最終製品のSDメモリカードやSSD(ソリッドステートドライブ)などが製品ラインアップだ。名が体を表すように、同社はメモリやストレージ領域に特化した事業を進めている。

そんな同社だが、メモリやストレージ領域に限らず幅広い領域で研究開発を進めているようだ。その一端は、半導体回路の国際会議である「A-SSCC 2018」(2018年11月5〜7日、台湾)で発表されたプロセッサ技術に垣間見える。

このプロセッサは、CNN(畳み込みニューラルネットワーク)の推論に特化したもの。演算の高速化と省エネルギー化を実現する、新しい最適量子化アルゴリズムとハードウェアアーキテクチャを有しており、演算スループットが従来比約5倍に向上し、消費エネルギーは同約5分の1まで低減可能という研究成果も得ている。

現業から離れているように見えるプロセッサの開発を通じ、東芝メモリは何を目指すのか。同プロセッサに関する投稿論文の筆頭著者である同社 システム技術研究開発センター システムコア技術開発第二部 主務の眞木明香氏を始め、同 回路設計主幹の藤本竜一氏と同 参事の宮下大輔氏に、今回発表された技術の概要と開発の狙いを聞いた。

ディープラーニング専用プロセッサに採用した2つの新技術

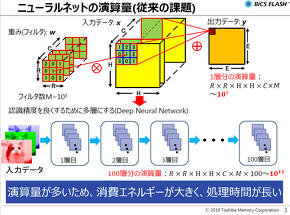

CNNなどディープラーニングの推論には多くの積和演算が発生し、その処理には一定レベルのコンピューティングパワーと電力が必要とされている。よって、推論精度に悪影響が発生しない程度に積和演算量を削減するアルゴリズムとともに、積和演算を高速かつ省エネルギーに実行できるプロセッサがあれば、ディープラーニングアプリケーションのさらなる普及が期待できる。

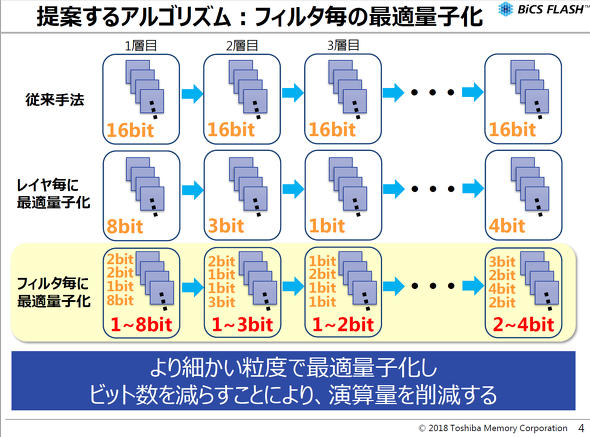

今回発表された新技術は2つとなる。それは、「フィルターごとの最適量子化アルゴリズム」と「ビットパラレル方式積和演算器」だ。

フィルターごとの最適量子化アルゴリズム

演算量の削減には、世界でさまざまな手法が提案されている。代表的なものとしては、アプリケーションの精度に寄与しないニューロンを刈り取るPruning(剪定)や、大規模なモデルを模擬するように小規模なモデルで学習させるDistillation(蒸留)、そして現在のディープラーニングアプリケーションで一般的に用いられているFP32(32ビット浮動小数点)やFP16よりサイズの小さい演算精度を用いるQuantization(量子化)などが挙げられる。

同社の研究チームは、演算量の削減に向けてウェイト(重み係数)の量子化に着目した。ウェイト量子化の先行研究では、ニューラルネットワーク内のそれぞれの隠れ層で量子化を行っており、演算精度は推論精度と演算量のトレードオフから最適なものを決定する。

一方で、CNNは隠れ層の中でも畳み込み層が画像の特徴抽出に重要な役割を果たしており、畳み込み層は複数のフィルターを持つ。そこで、同社では畳み込み層の各フィルターに量子化を行うアルゴリズムを提案した。このアルゴリズムでは先行研究よりもさらに細かい粒度で量子化するため、高い推論精度を維持しつつ演算量を削減できることがメリットだ。

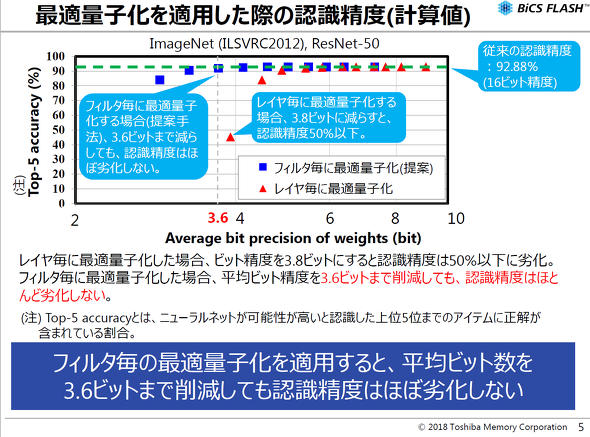

同研究チームは、画像分類問題で広く用いられているResNet-50を画像分類データセットImageNet(ILSVRC2012)で学習させ、16ビット固定精度、層ごとの量子化、そしてフィルターごとの量子化(提案アルゴリズム)の3種類の演算精度で推論精度の比較を行った。なお、推論精度の比較は、ニューラルネットワークが予測した上位5位のうちに正解が含まれている割合を表すTop-5 accuracyとしている。

この結果、提案アルゴリズムではモデル全体の平均演算精度を3.6ビットまで量子化させた場合においても16ビット固定精度とほぼ同等の推論精度を維持することを確認した。層ごとの量子化を行った場合には、モデル全体の平均演算精度を3.8ビットまで量子化させると推論精度が50%以下に劣化してしまうため、提案アルゴリズムの推論精度における優位性は明確であるという。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク