Armの半導体IPがタダで使える!? 「DesignStart」プログラムが拡充:組み込み開発ニュース(2/2 ページ)

ザイリンクス製FPGAで「Cortex-M1/M3」の無償利用が可能に

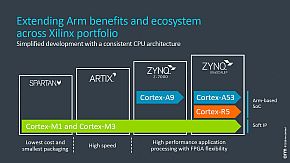

2018年10月から可能になったザイリンクス製FPGAでのCortex-M1とCortex-M3の無償利用については、ハードウェア設計についてはザイリンクスの開発環境「Vivado」上でドラッグ&ドロップするだけで可能である。ソフトウェア設計についても、Armの開発環境「KEIL」が対応しており、IAR Systemsも対応予定となっている。また、ハードウェアIPとしてArmのプロセッサコアを組み込んでいる「Zynq」に適用すれば、用途に応じてさまざまなプロセッサコアを搭載したSoCを設計できるようになるという。

「DesignStart」のザイリンクス製FPGAにおける「Cortex-M1」と「Cortex-M3」の利用プロセス(左)。「Zynq」に適用すれば、用途に応じてさまざまなプロセッサコアを搭載したSoCを設計できる(右)(クリックで拡大) 出典:Arm

「DesignStart」のザイリンクス製FPGAにおける「Cortex-M1」と「Cortex-M3」の利用プロセス(左)。「Zynq」に適用すれば、用途に応じてさまざまなプロセッサコアを搭載したSoCを設計できる(右)(クリックで拡大) 出典:Armなお、インテルなど他社製FPGAへの対応については「今回はザイリンクスからの話があったので先行して実現できた。今後は他社製FPGAでも可能性はある」(バー氏)としている。

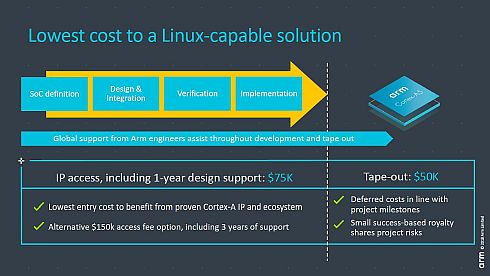

同じく2018年10月から利用できるCortex-A5は、DesigStartではLinuxに対応する初のプロセッサコアIPとなる。「Cortex-Aシリーズ」は他にもあるが「シングルボードコンピュータからリッチなIoTノード、医療機器、スマートホーム、ウェアら物端末に至るまで既に20億個を出荷している実績がある。そして多くのファウンドリの経験が高く、180〜7nmプロセスまで幅広い半導体製造プロセスに対応している。これらの理由からCortex-A5を選定した」(バー氏)という。

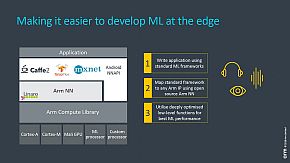

なお、Cortex-A5の性能は「Cortex-A7」の80%、「Cortex-A9」の70%程度だが、消費電力効率はCortex-A9の1.7倍に達する。4コアまでのマルチコア構成に対応するとともに、オープンソースソフトウェアの「Arm-NN」と組み合わせれば機械学習フレームワークのニューラルネットワークを実装することも可能だ。

DesignStartにおけるCortex-A5の利用料は、IPへのアクセスが7万5000米ドル(1年間のデザインサポート付き)、テープアウトが5万米ドルとなる(IC量産後のロイヤリティーは別)。ICの設計が完了した後のテープアウトにコストの比重を多めに配分しており「これによってユーザーはリスク低減が可能になる」(バー氏)としている。

なお、今回のCortex-A5の追加は、DesignStartベースで組み込みLinuxに対応するカスタムICを設計できるようにするところに狙いがある。バー氏は「組み込み機器の開発はLinuxもしくはAndroidに移行しつつあり、Armはその力を引き出せる。ぜひ多くの方に利用してもらいたい」と述べている。

関連記事

初歩から学ぶ、マイコン開発とARMプロセッサー

初歩から学ぶ、マイコン開発とARMプロセッサー

組み込みの世界では最も成功したプロセッサの1つ「ARM」を用いたマイコン開発にチャレンジします。クラウド開発環境「mbed」を使い、プログラムを書きながら回路をブレッドボードに実装、動作を確認しながらさまざまな内蔵デバイスの使い方をマスターしていきます。 Armの“囲い込まない”IoTプラットフォームがその先に見据えるもの

Armの“囲い込まない”IoTプラットフォームがその先に見据えるもの

このところ、IoTプラットフォームに関するArmの巻き返しがちょっとすごいことになっている。2018年2月下旬から矢継ぎ早に展開を急拡大しているのだ。 Armの「世界初」のIoTプラットフォームは何ができるのか

Armの「世界初」のIoTプラットフォームは何ができるのか

Armの日本法人アームは2018年8月22日、東京都内で会見を開き、トレジャーデータの買収に合わせて発表した新たなIoTプラットフォーム「Arm Pelion IoT Platform」について説明した。同日からパートナーなどを通して国内提供を始めている。 Armが考えるIoTの3つの課題とは、「Mbed」で可能性を広げていく

Armが考えるIoTの3つの課題とは、「Mbed」で可能性を広げていく

ArmのIoTサービスグループ プレジデントのディペッシュ・パテル氏が来日。パテル氏は「2025年に11兆米ドルもの市場規模になるといわれているIoTだが、『デバイスの多様性』『エンドツーエンドセキュリティ』『データの適切な利用』の3つが課題になる。Mbedを中心としたソリューションにより、IoTの可能性を広げていく」と語った。 ソフトバンクに買収されたArmの日本法人アームは「日本の経済に貢献する」

ソフトバンクに買収されたArmの日本法人アームは「日本の経済に貢献する」

ソフトバンクがプロセッサコアIP大手のArmを買収して1年強が経過した。親会社と同じ日本にあるArmの日本法人アームは、どのような事業展開を模索しているのだろうか。アーム社長の内海弦氏に、新たに注力しているIoT関連事業を中心に話を聞いた。 「ARM DesignStart」に「Cortex-M3」追加、設計開始時のライセンス費用も無償に

「ARM DesignStart」に「Cortex-M3」追加、設計開始時のライセンス費用も無償に

アームは、同社のプロセッサコアである「Cortex-M0」「Cortex-M3」の設計開始時のライセンス費用を無償化するなど、「ARM DesignStart」プログラムの強化について発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク