「業界最小」の消費電力でセキュリティも、サイプレスがIoT向け「PSoC」を投入:組み込み開発ニュース

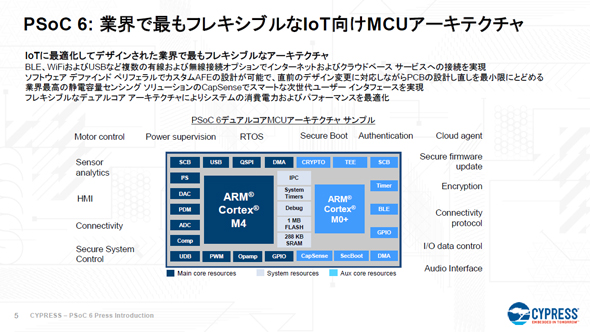

サイプレスセミコンダクタは、ウェアラブル端末や家電など幅広いIoTデバイスに向けたMCUアーキテクチャ「PSoC 6」を発表した。デュアルコア搭載で、動作周波数を切り替えることで消費電力を柔軟に低減する。静電容量タッチボタンや、ハードウェアベースのセキュリティの搭載にも対応している。

サイプレスセミコンダクタは2017年3月13日(現地時間)、ウェアラブル端末や家電など幅広いIoT(モノのインターネット)デバイスに向けたMCUアーキテクチャ「PSoC 6」を発表した。「ARM Coretex-M4」「ARM Coretex-M0+」のデュアルコア搭載で、動作周波数を切り替えることで消費電力を柔軟に低減する。また、低消費電力の40nmプロセスを採用している。

無線通信機能はオプションで、PSoC 6にBluetooth Low Energyを統合した「PSoC 6 BLE」を用意した他、Wi-Fiを別途組み合わせることもできる。静電容量タッチボタンや、データストレージを保護するハードウェアベースのセキュリティ「Trusted Execution Environment(TEE)」も搭載する。

既にサンプル出荷を開始しており、量産は2017年第4四半期初旬を計画している。

“中くらい”のIoTソリューション

PSoC 6は、ある程度のシステム制御ができる性能、低消費電力、セキュリティを同時実現することを目標に開発した。IoT向けのソリューションは、消費電力とコストがネックとなるハイエンドのプロセッサか、性能が不足するシングルコアMCUに二極化しており、その中間をターゲットとしている。

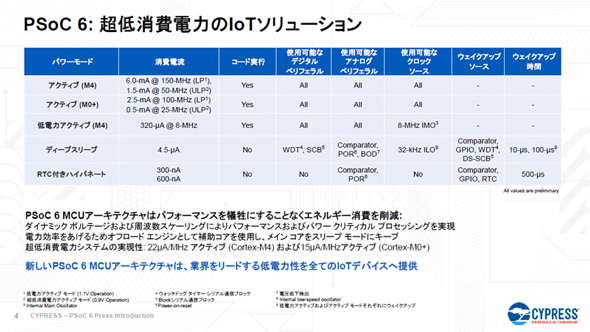

PSoC 6に搭載したARM Coretex-M4は150MHz、ARM Coretex-M0+は100MHzの周波数で動作する。40nmプロセスの採用により、消費電流はARM Coretex-M4の低電力アクティブパワーモードで320μA、CPUの処理を止めるディープスリープモードでは4.5μAを実現した。

電圧を動作モードに合わせて切り替える。処理が多い場合には電圧を上げて動作周波数を高くし、通信しない時は電圧を下げて消費電力を抑えることができる。

デュアルコアアーキテクチャを採用したことにより、メインコアのARM Coretex-M4をスリープ状態にしながらARM Coretex-M0+をオフロードエンジンとして使用することが可能なため消費電力を最適化したシステムデザインの実現に貢献する。

各CPUの分担としては、ARM Coretex-M4はOSの動作やHMIの表示、モーターの駆動といったシステムコントロールに、ARM Coretex-M0+はセキュアブートや省電力モードの駆動、通信機能に使い分けることを想定している。

Bluetooth Low Energy、Wi-FiやUSBなど無線・有線接続はオプションで、インターネットへの接続を実現する。ソフトウェアペリフェラルを使用することで、電子インクディスプレイなどのシステムコンポーネントカスタムアナログフロントエンドやデジタルインタフェースを設計できる。また、サイプレスの静電容量センサー技術で防水の「CapSense」の最新世代を搭載している。

家電にもセキュリティ

セキュリティ面では、セキュアブート機能に加え、ファームウェア、アプリケーション、暗号キーなどのセキュアアセットを保護するためのデータストレージを備えたハードウェアベースのTEEを提供する。外部メモリや部品を追加することなく複数のセキュリティ環境を同時にサポートできる。業界標準の暗号化アルゴリズムのECC(Elliptical-Curve Cryptography)やAES(Advanced Encryption Standard)をハードウェア コプロセッサとして搭載する。

PSoC 6は、ウェアラブル端末からファクトリーオートメーションまでIoT向けに幅広く用途を見込んでいるが、家電であってもセキュリティが重視される傾向に対応して安全性を強化した。

関連記事

サイプレスが車載マイコンに40nmプロセスを初採用、低価格メータークラスタ向け

サイプレスが車載マイコンに40nmプロセスを初採用、低価格メータークラスタ向け

サイプレス セミコンダクタは車載マイコン「Traveoファミリ」の新製品を発表した。同社初となる40nmプロセスで製造する。量販車種のメータークラスタや、複雑化する車載ネットワークのゲートウェイに向ける。Traveoファミリに最適な電源ICや、日本発の車載LAN規格「CXPI」対応のトランシーバICなども併せて供給する。 音声認識の覇権を握る「Amazon Alexa」、逆転の余地はまだある?

音声認識の覇権を握る「Amazon Alexa」、逆転の余地はまだある?

「CES 2017」で一躍存在感を高めた音声認識インタフェース「Amazon Alexa」。既に覇権を握りつつあるという見方も多い。それでも競合他社にとってまだ逆転の余地は残されているようだ。 IoT時代に対応するWi-Fiセキュリティガイドを公開

IoT時代に対応するWi-Fiセキュリティガイドを公開

トレンドマイクロは、Wi-Fi提供事業者および利用者向けに、Wi-Fi環境におけるセキュリティの脅威と対策を解説した「IoT時代を見据えたWi-Fiセキュリティガイド」を公開した。 急速に普及しつつある「LoRa」

急速に普及しつつある「LoRa」

既に27カ国、150の地域でサービスが始まっている「LoRa」について紹介する。「SIGFOX」など他のLPWAN(Low-Power Wide Area Network)との違いはどこにあるのか。LoRaの普及状況や課題などとともに見ていく。 ホームアシスタントデバイス「Google Home」は“どうやって”家族を手助けするか

ホームアシスタントデバイス「Google Home」は“どうやって”家族を手助けするか

2016年5月に発表された、Googleのホームアシスタントデバイス「Google Home」。Amazon Echo対抗と目されるが、同じくGoogleの「Project Brillo」とも関連づけて考えるべきだろう。

Copyright © ITmedia, Inc. All Rights Reserved.